Efinix FPGA-k használata AI/ML képalkotáshoz - 2. rész: Képfelvétel és képfeldolgozás

Contributed By DigiKey's European Editors

2023-05-05

Szerkesztői megjegyzés: Az új megközelítések szerint gyártott FPGA-architektúrák finomabb vezérlési képességeket és nagyobb rugalmasságot biztosítanak a gépi tanulási (ML) és a mesterséges intelligencia (AI) iránti igények kielégítésére. Kétrészes cikksorozatunk 1. része egy ilyen architektúrát mutat be az Efinix-től, és azt, hogyan kezdhető meg vele a munka egy fejlesztői kártya segítségével. Ebben a 2. részben a fejlesztői kártya külső eszközökkel és perifériákkal (például kamerával) való összekapcsolását tárgyaljuk, valamint azt, hogyan lehet az FPGA-t kihasználni a képfeldolgozási szűk keresztmetszetek megszüntetésére.

Az FPGA-knak kritikus szerepe van számos rendszeren belül, az ipari vezérlési és biztonságtechnikai rendszerektől kezdve a robotikán át a repülésig, űrkutatásig és autóiparig. Rugalmas programozható logikai struktúrájuknak és széleskörű kapcsolódási képességeiknek köszönhetően az FPGA-k egyik növekvő felhasználási területe a képfeldolgozás, ahol a gépi tanulás (ML) alkalmazható. Párhuzamos logikai felépítésüknek köszönhetően az FPGA-k ideálisak olyan megoldások megvalósítására, amelyek több nagysebességű kamerainterfészt tartalmaznak. Ezenkívül az FPGA-k logikai szerkezete lehetővé teszi dedikált adatfeldolgozó csatornák (pipeline-ok) használatát is, ezáltal kiküszöbölve a szűk keresztmetszeteket, amelyek a CPU- vagy GPU-alapú megoldásoknál a megosztott erőforrások miatt fordulnak elő.

Az Efinix Titanium FPGA-k ezen másodszori tárgyalásakor megvizsgáljuk a Ti180 M484 fejlesztői kártyához tartozó referencia képfeldolgozó alkalmazást. A cél: a rendszert alkotó elemek működésének megértése és megismerése, és annak azonosítása, hogy az FPGA-re épülő technológia hol teszi lehetővé a szűk keresztmetszetek megszüntetését, illetve hol biztosít más előnyöket a fejlesztők számára.

A Ti180 M484-re épülő referencia kártya

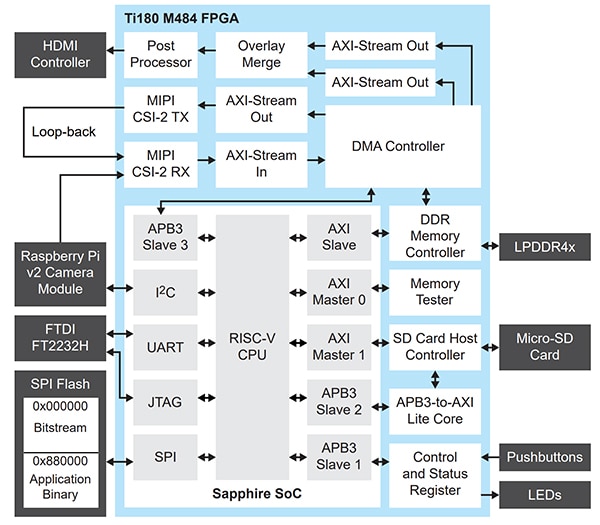

A működési elvet tekintve a referencia kártya (1. ábra) több MIPI (Mobile Industry Processor Interface) kamerától fogadja a képeket, az LPDDR4x-ben képkockapufferelést végez, majd a képeket egy HDMI (High Definition Multimedia Interface) kijelzőre adja ki. A kamera-bemeneteket és a HDMI-kimenetet egy FPGA-val rendelkező NyÁK-csatlakozós kártya (FPGA Mezzanine Card, FMC) és az alaplapon lévő négy Samtec QSE interfész biztosítja.

1. ábra: Működési elvét tekintve a Ti180 M484 referencia kártya több MIPI-kamerától fogadja a képeket, az LPDDR4x-ben képkockapufferelést végez, majd a képeket egy HDMI-kijelzőre küldi ki (kép: Efinix)

1. ábra: Működési elvét tekintve a Ti180 M484 referencia kártya több MIPI-kamerától fogadja a képeket, az LPDDR4x-ben képkockapufferelést végez, majd a képeket egy HDMI-kijelzőre küldi ki (kép: Efinix)

Az FMC - QSE bővítőkártyát a HDMI kiegészítő kártyával együtt használják a kimeneti video útvonal biztosításához, míg a három QSE csatlakozót a DFRobot SEN0494 MIPI kameráihoz való kapcsolódáshoz. Ha nem áll rendelkezésre több MIPI-kamera, egyetlen kamera is használható az egyetlen kameracsatorna visszahurkolásával további kamerák szimulálására.

Magas szintről nézve ez a rendszer egyszerűnek tűnhet, de több nagy felbontású (HD) MIPI-adatfolyam nagy képkockasebességgel történő fogadása azonban nem egy egyszerű feladat. Itt mutatkozik meg az FPGA-technológia előnye, mivel lehetővé teszi a tervezők számára egyszerre több MIPI-folyam párhuzamos feldolgozását.

A referencia kártya architektúrája lehetővé teszi mind a párhuzamos, mind a szekvenciális feldolgozási struktúrák kihasználását az FPGA-val. A párhuzamos struktúrákat a képfeldolgozó pipeline megvalósítására használják, míg egy RISC-V processzor biztosítja az FPGA hivatkozási táblázatainak (LUT) szekvenciális feldolgozását.

A képfeldolgozó pipeline számos FPGA-alapú képfeldolgozó rendszerben két részre osztható, nevezetesen a bemeneti és a kimeneti folyamra. A bemeneti adatfolyam a kamera/érzékelő interfészhez csatlakozik, és az érzékelő kimeneti jelét képfeldolgozó funkciókkal manipulálják. Ez lehet többek között Bayer-konverzió, automatikus fehéregyensúly és egyéb képminőség-javító funkciók. A kimeneti folyamban a rendszer előkészíti a képet a megjelenítésre. Ez magában foglalja a színtér-konverziót (pl. RGB-ből YUV-ba) és a kívánt kimeneti formátumhoz, például HDMI-hez szükséges utófeldolgozást.

Gyakran előfordul, hogy a bemeneti képfeldolgozási lánc az érzékelő képpont-órajelének megfelelő sebességgel működik. Ennek időzítése eltér a kimeneti láncétól, amelynek feldolgozása a kimeneti kijelző frekvenciáján történik.

A bemenet és a kimeneti feldolgozási pipeline összekapcsolására egy keretpuffer szolgál, amelyet gyakran egy külső nagy teljesítményű memóriában, például LPDDR4x memóriában tárolnak. Ez a keretpuffer szétválasztja a bemeneti és kimeneti pipeline-okat, így a keretpuffer közvetlen memóriaeléréssel elérhető a megfelelő órajelfrekvencián.

A Ti180 referencia kártya a fent vázolt koncepciókhoz hasonlóan működik. A bemeneti képfeldolgozó pipeline egy MIPI Camera Serial Interface 2 (CSI-2) vevő IP (szellemi tulajdon) mag, amely a Titanium FPGA MIPI fizikai rétegével (MIPI D-PHY) kompatibilis be- és kimenetekre (I/O) épül. A MIPI egy nem egy minden kihívástól mentes interfész, mivel egyidejűleg használ közös földpontú és differenciális jelátvitelt ugyanazon a differenciális páron, valamint alacsony és nagysebességű kommunikációt is. A MIPI D-PHY-nek az FPGA I/O-ba történő integrálása csökkenti az áramköri kártya tervezésének összetettségét, és egyben csökkenti az anyagköltséget (BOM) is.

A kamerából érkező képfolyam fogadása után a referencia kártya ezután a MIPI CSI-2 RX kimenetét átalakítja egy Advanced eXtensible Interface (AXI) Stream adatfolyammá. Az AXI Stream egy mester-szolga irányú egyirányú, nagy sebességű adatátviteli interfész. A mester és a szolga közötti átvitelhez kézfogási jelek (tvalid és tready), valamint oldalsáv-jelek állnak rendelkezésre. Ezek az oldalsáv-jelek felhasználhatók a kép időzítési információinak, például a képkocka kezdetének és a sor végének továbbítására.

Az AXI Stream ideális képfeldolgozási használathoz, és lehetővé teszi az Efinix számára, hogy védett képfeldolgozást (IP-ket) kínáljon, amelyek az adott felhasználási eset igényei szerint könnyen integrálhatók a feldolgozási láncba.

A fogadás után a MIPI CSI-2 képadatokat és az időzítési jeleket AXI Stream-be konvertálják, és egy közvetlen memória-hozzáférési (DMA) modulba táplálják be, amely a képkockát az LPDDR4x-be írja, és a képkocka puffereként működik.

Ezt a DMA-modult a Sapphire egylapkás (SoC) rendszerében található FPGA-ban lévő RISC-V mag vezérli. Ez az SoC biztosítja a vezérlést, például a DMA-írások leállítását és elindítását, továbbá a DMA-író csatornának a képadatok LPDDR4x-be történő helyes írásához szükséges információkkal való ellátását. Ez tartalmazza a memóriahelyre, valamint a kép bájtokban meghatározott szélességére és magasságára vonatkozó információkat is.

A referencia kártya kimeneti csatornája a RISC-V SoC által vezérelve olvassa be a képinformációkat az LPDDR4x keretpufferből. Az adatokat a DMA IP AXI Stream-ként adja ki, majd az érzékelő által szolgátatott RAW formátumból RGB formátumba konvertálja (2. ábra) és előkészíti a kimenetre az Analog Devices kártyára integrált ADV7511 HDMI-adójával.

2. ábra: A referencia kártya kimeneti mintaképei (kép: Adam Taylor)

2. ábra: A referencia kártya kimeneti mintaképei (kép: Adam Taylor)

A DMA használata azt is lehetővé teszi, hogy a Sapphire SoC RISC-V hozzáférjen a képkockapufferben tárolt képekhez, valamint az absztrakt statisztikákhoz és a képinformációkhoz. A Sapphire SoC képes arra is, hogy az LPDDR4x-be overlayeket írjon, így azok a kimeneti videófolyamba is beolvadhatnak.

A modern CMOS-képérzékelők (CIS-ek) többféle üzemmóddal rendelkeznek, és úgy konfigurálhatók, hogy chipen belüli feldolgozást valamint többféle kimeneti formátumot és órajelezési sémát biztosítsanak. Ezen konfigurálás általában egy I²C interfészen keresztül történik. Az Efinix referencia kártyája esetén ezt az I²C-kommunikációt a Sapphire SoC RISC-V processzor biztosítja a MIPI-kamerákhoz.

A RISC-V processzornak a Titanium FPGA-ba történő integrálása csökkenti a végső megoldás teljes méretét, mivel így nincs szükség sem összetett FPGA állapotgépek megvalósítására, amelyek növelik a tervkockázatot, sem pedig külső processzorokra, amelyek növelik a BOM-ot.

A processzor beépítése továbbá lehetővé teszi a MicroSD-kártyával való kommunikációhoz szükséges további IP-k használatát is. Ennek köszönhetően a referencia kártya olyan valós helyzetekben is használható, ahol a képeket későbbi elemzés céljából tárolni kell.

Összességében a Ti180 referencia kárya architektúráját úgy optimalizálták, hogy egy kompakt, alacsony költségű, ugyanakkor nagy teljesítményű megoldás legyen, amely lehetővé teszi a fejlesztők számára, hogy rendszerintegráció révén csökkentsék a BOM-költségeket.

A referenciatervek egyik legfontosabb előnye, hogy felhasználhatók saját egyedi hardvereken történő fejlesztések beindításához, lehetővé téve a fejlesztők számára a már kész referencia kialakítás kritikus elemeinek átvételét és a szükséges testreszabásokkal való kiegészítését. Ez azt is jelenti, hogy az Efinix TinyML flow-ja felhasználható az FPGA-n futó, látásalapú TinyML-alapú működés megvalósításához. Ezzel kihasználható az FPGA-logika párhuzamos jellege és az a lehetőség, hogy a RISC-V processzorokba könnyen hozzáadhatók egyéni utasítások, így az FPGA-logikán belül gyorsítók is létrehozhatók.

Megvalósítás

Amint azt az 1. részben tárgyaltuk, az Efinix architektúrája egyedülálló abban a tekintetben, hogy XLR (eXchangeable Logic and Routing) cellákat használ az útválasztási és logikai funkciók biztosítására. Egy olyan videorendszer, mint ez a referencia kártya egy vegyes rendszer, amely egyszerre logikailag és az útválasztást tekintve is komplex: széleskörű és komplex logikai műveletekre van szükség a képfeldolgozási funkciók megvalósításához, és szintén bonyolult útválasztásra van szükség az IP-cellák szükséges frekvenciákon történő összekapcsolásához.

A referencia kártya az eszközön belüli XLR cellák körülbelül 42%-át használja, így bőséges hely marad a kiegészítésekre, beleértve az egyedi alkalmazási lehetőségeket, mint például a peremhálózati gépi tanulás (ML) megvalósítását.

A blokk-RAM és a digitális jelfeldolgozó (DSP) blokkok foglaltsága tekintetében az elrendezés szintén nagyon hatékony, a 640 DSP blokkból csak 4 van használatban, a memóriablokkoknak pedig 40%-a (3. ábra).

|

3. ábra: Az Efinix architektúra erőforrás-elosztása azt mutatja, hogy az XLR-celláknak csak 42%-a van kihasználva, így bőséges hely marad további folyamatok számára (kép: Adam Taylor)

Az eszköz bemeneti/kimeneti felületén az LPDDR4x DDR-interfészét használják a Sapphire SoC alkalmazásmemóriájának és a képkockapuffereknek a biztosítására. Az eszközhöz kötött összes MIPI-erőforrás és a fáziszárt hurkok 50%-a ki van használva (4. ábra).

|

4. ábra: Pillanatkép a használt interfészről és a bemeneti/kimeneti erőforrásokról (kép: Adam Taylor)

Az általános célú I/O (GPIO) az I²C kommunikáció biztosítására szolgál a Sapphire SoC-hez csatlakoztatott számos interfésszel együtt, beleértve a NOR FLASH, az USB UART és az SD-kártyát. A HSIO a nagysebességű videokimenet biztosítására szolgál az ADC7511 HDMI-adó számára.

Az FPGA-k használatának egyik döntő eleme nemcsak a feladat FPGA-n belüli megvalósítása és annak oda való beillesztése, hanem az is, hogy a megvalósított logika elhelyezhető legyen az FPGA-n belül, és az üzenetküldés során elérje a kívánt időzítési teljesítményt.

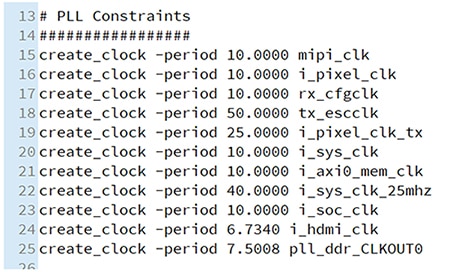

Régen elmúltak már azok a napok, amikor egyetlen órajeles FPGA-struktúrák voltak használatban. A Ti180 referencia kártya több különböző órajellel rendelkezik, amelyek mindegyike magas frekvencián fut. A végső időzítési táblázatban láthatók a rendszeren belüli órajelek maximális frekvenciái. Itt a kért időzítési teljesítmény látható az időkorlátokban is (5. ábra), amelyeknél a maximális órajelfrekvencia 148,5 MHz a kimeneti HDMI-órajel esetében.

5. ábra: A referencia kártya órajel-korlátai (kép: Adam Taylor)

5. ábra: A referencia kártya órajel-korlátai (kép: Adam Taylor)

A korlátok figyelembevételével megvalósított időzítés mutatja a Titanium FPGA XLR-struktúrája által kínált lehetőségeket, mivel csökkenti a lehetséges útválasztási késleltetést, ezáltal növelve a megvalósítás működési teljesítményét (6. ábra).

|

6. ábra: A korlátok figyelembevételével megvalósított időzítés mutatja a Titanium FPGA XLR-struktúrája által kínált lehetőségeket a lehetséges útválasztási késleltetés csökkentésére, ezáltal növelve a megvalósítás működési teljesítményét (kép: Adam Taylor)

Összegzés

A Ti180 M484 referencia kártya egyértelműen bemutatja az Efinix FPGA-k, ez esetben a Ti180 képességeit. A kártyával megvalósított kialakítás az egyedi I/O struktúrák hasznosítására épül, egy több bejövő MIPI folyamot támogató komplex képfeldolgozási útvonal megvalósítására. Ezt a képfeldolgozó rendszert egy soft-core Sapphire SoC vezérli, amely megvalósítja az adott alkalmazási feladat esetén szükséges szekvenciális feldolgozási elemeket.

Disclaimer: The opinions, beliefs, and viewpoints expressed by the various authors and/or forum participants on this website do not necessarily reflect the opinions, beliefs, and viewpoints of DigiKey or official policies of DigiKey.