Efinix FPGA-k használata mesterséges intelligenciás és gépi tanulásos képalkotáshoz – 1. rész: Az első lépések

Contributed By DigiKey's European Editors

2023-04-20

A szerkesztő megjegyzése: Az újfajta FPGA-architektúrák finomabb vezérlést és nagyobb rugalmasságot kínálnak a gépi tanulás (ML, machine learning) és a mesterséges intelligencia (MI vagy az angol artificial intelligence kifejezésből alkotott betűszóval AI) támasztotta igények kielégítése terén. A kétrészes sorozat 1. része az Efinix egyik ilyen architektúráját mutatja be, és ismerteti, hogyan lehet fejlesztőkártya használatával nekikezdeni a fejlesztésnek. A 2. rész a fejlesztőkártya külső eszközökkel és perifériákkal, például kamerával való összekapcsolását tárgyalja.

Az FPGA-k (field programmable gate array, helyben programozható logikai kapumátrix) számos felhasználási területen kritikus szerepet játszanak, az ipari vezérléstől és biztonságtól kezdve a robotikán át a repülésig, az űrkutatásig és a gépjárműiparig. A programozható logikai magok rugalmas jellegének és sokféle csatlakozási lehetőségének köszönhetően az FPGA-k egyik egyre növekvő felhasználási területe a képfeldolgozás, ahol gépi tanulási következtetéseket kell használni. Az FPGA-k ideálisak olyan készülékek létrehozására, amelyek több nagy sebességű kameracsatlakozóval vannak ellátva. Az FPGA-k emellett lehetővé teszik célorientált feldolgozó futószalagok kialakítását is a logikán belül, kiküszöbölve ezzel a CPU- vagy GPU-alapú megoldásokhoz kapcsolódó szűk keresztmetszeteket.

Sok fejlesztő esetében azonban a tervezett készülékek több gépi tanulási vagy mesterséges intelligenciás funkciót és finomabb vezérlést vagy útválasztást és logikát igényelnek, mint amit a programozható logikai blokkokkal (CLB, configurable logic block) ellátott hagyományos FPGA-architektúrák kínálni tudnak. Az újabb FPGA-architektúrák kezelik ezeket a problémákat. Az Efinix Quantum architektúrája például egy XLR (eXchangeable Logic and Routing, cserélhető logika és útválasztás) blokkot használ.

Ez a cikk az Efinix FPGA-architektúrájának legfontosabb jellemzőit és tulajdonságait tárgyalja, kiemelve annak mesterséges intelligenciás és a gépi tanulási képességeit, és bemutatva néhány tényleges megvalósítást. Ezután egy olyan fejlesztőkártyát és az ahhoz kapcsolódó eszközöket ismertet, amelyekkel a fejlesztők gyorsan elkezdhetik a következő mesterséges intelligenciás vagy gépi tanulásos képalkotó készülék tervezését.

Efinix FPGA-eszközök

Az Efinix jelenleg két ilyen termékcsaládot kínál. Elsőként a Trion termékcsaládot mutatta be, amely 4000 és 120 ezer logikai elem (LE, logic element) közötti logikai sűrűséget kínál, és SMIC 40LL eljárással készül. A legújabb Titanium termékcsalád 35 000 és 1 millió logikai elem közötti logikai sűrűséggel készül, és a nagyon népszerű TSMC 16 nm-es csomópontra épül.

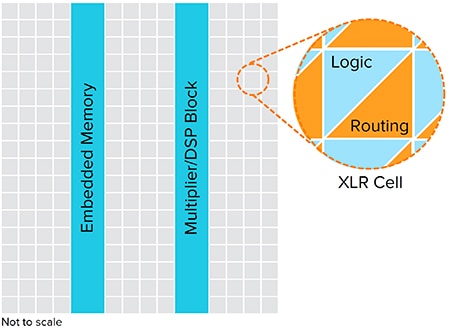

Mindkét termékcsalád a Quantum architektúrára épül, amely egyedülálló az FPGA-k világában. A szabványos FPGA-architektúrák programozható logikai blokkokon alapulnak, amelyek a legegyszerűbb szinten egy indextáblát (LUT) és bistabil billenőáramköröket tartalmaznak. A programozható logikai blokkokok logikai egyenleteket hajtanak végre, amelyeket aztán útválasztás révén kapcsolnak össze egymással. Az Efinix Quantum architektúrája az XLR blokk használatával eltávolodik a különálló logikai és útválasztó blokkoktól.

Az XLR blokkot az teszi egyedivé, hogy programozható úgy, hogy indextáblával ellátott logikai cellaként, regiszterként és összeadóegységként vagy útválasztó mátrixként működjön. Ez a megoldás finomabban szabályozható architektúrát kínál, amely rugalmasabb útválasztást tesz lehetővé, ez pedig módot ad arra, hogy olyan eszközöket lehessen létrehozni, amelyek nagy logikai terheléssel vagy sok útválasztási feladattal érik el a kívánt teljesítményt.

1. ábra: Az XLR blokkot az teszi egyedivé, hogy programozható úgy, hogy indextáblával ellátott logikai cellaként, regiszterként és összeadóegységként vagy útválasztó mátrixként működjön (kép: Efinix)

1. ábra: Az XLR blokkot az teszi egyedivé, hogy programozható úgy, hogy indextáblával ellátott logikai cellaként, regiszterként és összeadóegységként vagy útválasztó mátrixként működjön (kép: Efinix)

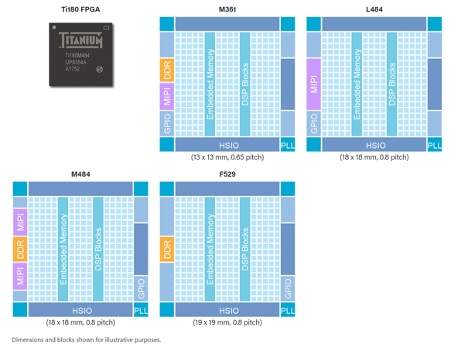

Legújabb termékcsaládként a Titanium eszközök kínálják a legfejlettebb funkciókat a fejlesztők számára (2. ábra). Az XLR maggal együtt több gigabit/másodperc (Gb/s) átviteli sebességű soros kapcsolatokat tesznek lehetővé, amelyek a választott eszköztől függően 16 Gb/s vagy 25,8 Gb/s átviteli sebességgel működnek. Ezek a több Gb/s-es kapcsolatok elengedhetetlenek a lapkán belüli és kívüli nagy sebességű adatátvitel lehetővé tételéhez.

2. ábra: A Titanium FPGA Ti180 többféle változatban kapható a sínszélesség, a szükséges be- és kimenetek és a memóriaigény függvényében (kép: Efinix)

2. ábra: A Titanium FPGA Ti180 többféle változatban kapható a sínszélesség, a szükséges be- és kimenetek és a memóriaigény függvényében (kép: Efinix)

A Titanium eszközök a be- és kimeneti (I/O) csatlakozók széles skáláját kínálják, amelyek általános célú I/O (GPIO) csoportba sorolhatók, és képesek támogatni a közös földpontú (single ended) be- és kimeneti szabványokat, például a 3,3 V-os, 2,5 V-os és 1,8 V-os kisfeszültségű CMOS-okat (LVCMOS, low-voltage CMOS).

A nagy sebességű és különbségi jelátvitelhez a Titanium eszközök nagy sebességű be- és kimenetet (HSIO, high-speed I/O) kínálnak, amely támogatja az olyan közös földpontú be- és kimeneti szabványokat, mint az 1,2 V-os és 1,5 V-os LVCMOS, valamint az SSTL és a HSTL. A nagy sebességű be- és kimenet által támogatott különbségi be- és kimeneti szabványok közé tartozik a kisfeszültségű különbségi jelátvitel (LVDS, low-voltage differential signaling), valamint a különbségi SSTL és a HSTL.

A korszerű FPGA-khoz szorosan csatolt nagy sávszélességű memóriára is szükség van, amely a képfeldolgozó alkalmazások képkockáinak és a jelfeldolgozáshoz szükséges mintaadatoknak a tárolására és természetesen az FPGA-ban kialakított processzorok operációs rendszereinek és szoftverének futtatására szolgál. A Titanium eszközcsalád lehetővé teszi a DDR4 (double data rate 4, kétszeres adatelérési sebességű, 4. generációs) és az LPDDR4(x) (kis fogyasztású DDR4(x), low-power DDR4(x)) memória használatát. A választott Titanium eszköztől függően a támogatott sínszélesség x32 (J) vagy x16 (M), míg egyes eszközök nem támogatják az LPDDR4-et (L).

A Titanium FPGA-k SRAM-alapúak, és beállítási memóriát igényelnek, az eszköz beállítása pedig vagy a gazda/szolga soros perifériás illesztőfelület (master/slave Serial Peripheral Interconnect, SPI), vagy a JTAG segítségével történik. A beállítási módszer biztonságának megteremtése érdekében a Titanium FPGA AES GCM titkosítással titkosítja a bitfolyamot, valamint AES GCM és RSA-4096 titkosítást használ a bitfolyam hitelesítésére. Ehhez hasonló erős biztonságra van szükség, mert az FPGA-kat helyi eszközökben (más néven peremeszközökben) használják, ahol a rosszindulatú szereplők hozzájuk férhetnek, és károsan befolyásolhatják a viselkedésüket.

A fejlesztőkártya ismertetése

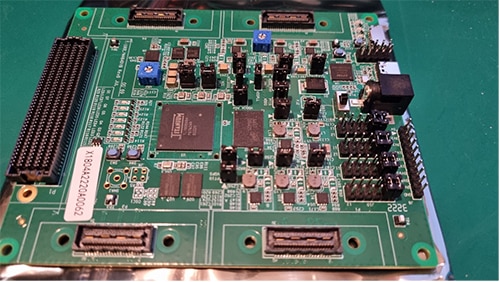

A fejlesztőkártyák az FPGA-k értékelési folyamatának fontos elemét képezik, mert az eszköz és a felhasználásával készült készülékprototípusok képességeinek feltárására használhatók, segítve ezzel az általános kockázat csökkentését. A Titanium FPGA-k kiértékeléséhez és a prototípusok elkészítéséhez rendelkezésre álló első fejlesztőkártya a Ti180 M484 (3. ábra). A kártyán egy FPGA Mezzanine Card (FMC) csatlakozó és négy Samtec QSE csatlakozó található.

3. ábra: A Titanium FPGA-t tartalmazó Ti180 M484 fejlesztőkészlet egy FMC csatlakozóval és négy Samtec QSE csatlakozóval van felszerelve (kép: Adam Taylor)

3. ábra: A Titanium FPGA-t tartalmazó Ti180 M484 fejlesztőkészlet egy FMC csatlakozóval és négy Samtec QSE csatlakozóval van felszerelve (kép: Adam Taylor)

A fejlesztőkártyára szerelt Ti180 FPGA 172 ezer XLR cellát, 32 globális órajelet, 640 digitális jelfeldolgozó (DSP) elemet és 13 MB beágyazott RAM-ot kínál. A digitális jelfeldolgozó elemek fixpontos 18 × 19 bites szorzások és 48 bites szorzások végrehajtását teszik lehetővé. Ez a digitális jelfeldolgozó optimalizálható két- vagy négycsatornásként futó egyutasításos, többadatos (SIMD, single instruction, multiple data) műveletekre is. A digitális jelfeldolgozó elemek beállíthatók lebegőpontos műveletek végzésére is.

Mint a legtöbb fejlesztőkártyán, a Ti180-on is vannak egyszerű LED-ek és gombok. Az igazi ereje azonban a csatlakozási képességeiben rejlik. A Ti180 fejlesztőkártya egy kis érintkezőszámú FMC csatlakozóval van felszerelve, amely perifériák széles körének csatlakoztatását teszi lehetővé. Mivel ez egy széles körben használt szabvány, sokféle FMC-kártya létezik, amelyek nagy sebességű analóg-digitális átalakítók (ADC), digitális-analóg átalakítók (DAC), hálózatok, valamint memóriák és tárolók csatlakoztatására adnak lehetőséget.

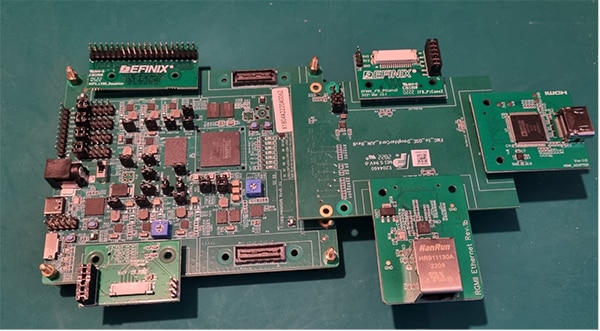

A kártya az FMC csatlakozón kívül négy Samtec QSE csatlakozót is tartalmaz, amelyek segítségével a fejlesztők bővítőkártyákat adhatnak az fejlesztőkártyához. Ezek a QSE csatlakozók MIPI (Mobile Industry Processor Interface, mobil ipari feldolgozási csatlakozó) be- és kimenetekként szolgálnak, mindegyik QSE csatlakozó egy MIPI be- vagy kimenet kínál.

4. ábra: A képen a Ti180 M484 fejlesztőkészlet látható a QSE és FMC csatlakozókon alapuló sokoldalú bővítési lehetőségekkel (kép: Adam Taylor)

4. ábra: A képen a Ti180 M484 fejlesztőkészlet látható a QSE és FMC csatlakozókon alapuló sokoldalú bővítési lehetőségekkel (kép: Adam Taylor)

A Ti180 kártya 256 MB LPDDR4 memóriát is tartalmaz, ezzel támogatva a nagy teljesítményű memóriát igénylő kép- vagy jelfeldolgozó alkalmazásokat. Ezenkívül a fejlesztőkártya többféle – 25, 33,33, 50 és 74,25 MHz-es – órajelet is szolgáltat, amelyek az eszköz fáziszárt hurkával (PLL, phase locked loop) különböző belső frekvenciák létrehozására használhatók.

A fejlesztés során rendkívül fontos, hogy a kártyán élőben lehessen újraprogramozást és hibakeresést végezni, amihez JTAG-kapcsolatra van szükség, ezt a kártya USB-C csatlakozóján keresztül lehet megvalósítani. Található a kártyán két 256 MB-os nem felejtő, NOR típusú flashmemória is, amelyek a beállítási megoldás szemléltetésére használhatóak.

A kártya áramellátása egy 12 V-os univerzális hálózati adapterről történik, amely szintén megtalálható a kártya dobozában. A készlet részét képezi még egy FMC–QSE külső átalakító csatlakozódoboz, valamint QSE-alapú, HDMI-, Ethernet-, MIPI- és LVDS-csatlakozójú bővítőkártyák is. A Ti180 képfeldolgozási képességeinek bemutatására egy kétcsatornás Raspberry Pi (RPI) kiegészítőkártya és két IMX477 kamerakártya is található a készletben.

A szoftverkörnyezet

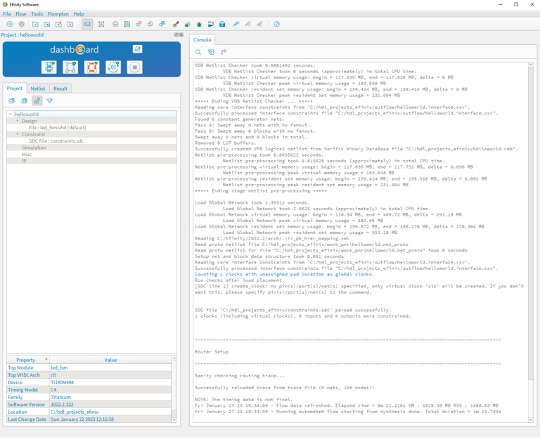

A Ti180 fejlesztőkártyára épülő tervek megvalósításához használhatja az Efinix cég Efinity szoftverét. A szoftver lehetővé teszi bitfolyam előállítását szintézis, valamint az alkatrész-elhelyezés és vezetőcsík-vonalvezetés megtervezése segítségével. Emellett kínál még a fejlesztők számára szellemitulajdon-blokkokat, időzítéselemzést és lapkán belüli hibakeresést is.

Vegye figyelembe, hogy az Efinity szoftverhez való hozzáféréshez fejlesztőkártya szükséges. Más gyártókkal ellentétben azonban ennek a szoftvereszköznek nincsenek különböző verziói, amelyek további licenceket igényelnének.

Az Efinity szoftveren belül új projekteket lehet létrehozni a választott eszközhöz. Az RTL (regiszterátviteli szintű, register-transfer level) fájlok ezután hozzáadhatók a projekthez, és létrehozhatók az időzítéshez és a be- és kimenetek tervezéséhez szükséges korlátozások. A fejlesztők elvégezhetik az Efinityn belül a be- és kimenetek tervezését is, felhasználva a HSIO-t, a GPIO-t és a speciális a be- és kimeneti eszközöket.

5. ábra: Az Efinity szoftveren belül új projekteket lehet létrehozni a választott eszközhöz (kép: Adam Taylor)

5. ábra: Az Efinity szoftveren belül új projekteket lehet létrehozni a választott eszközhöz (kép: Adam Taylor)

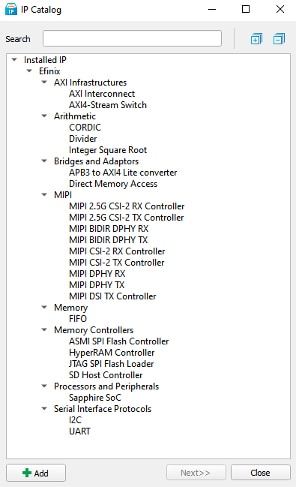

Az FPGA-tervezés kritikus eleme a szellemi tulajdon felhasználása, különösen az olyan összetett szellemi tulajdonok esetében, mint az AXI-összeköttetések, a memóriavezérlők és a szoftveresen kialakított (softcore) processzorok. Az Efinity számos szellemitulajdon-blokkot bocsát a fejlesztők rendelkezésére, amelyekkel felgyorsítható a tervezési folyamat.

6. ábra: Az Efinity egy szellemitulajdon-katalógust bocsát a fejlesztők rendelkezésére, amelyet felhasználhatnak a tervezési folyamat felgyorsítására (kép: Adam Taylor)

6. ábra: Az Efinity egy szellemitulajdon-katalógust bocsát a fejlesztők rendelkezésére, amelyet felhasználhatnak a tervezési folyamat felgyorsítására (kép: Adam Taylor)

Bár az FPGA-k kiválóan alkalmasak párhuzamos feldolgozási struktúrák létrehozására, sok FPGA tartalmaz szoftveresen kialakított (softcore) processzorokat. Ezek lehetővé teszik a sorrendi feldolgozás, például a hálózati kommunikáció megvalósítását. A szoftveresen kialakított processzorok Efinix eszközökbe való beépítésének lehetővé tételéhez az Efinity a Sapphire egylapkás rendszerként (SoC, system on a chip) megvalósított beállítóeszközt kínálja. A Sapphire lehetővé teszi a fejlesztők számára, hogy olyan többprocesszoros rendszert definiáljanak, amelyekre egyaránt jellemzőek a több processzorhoz tartozó gyorsítótárak és az egységes gyorsítótár-tartalom (más néven gyorsítótár-koherencia), valamint képesek valamilyen beágyazott Linux operációs rendszer futtatására is. A Sapphire-on belül a fejlesztő egy–négy szoftveresen kialakított processzor közül választhat.

Az így megvalósított softcore processzor a VexRiscV szoftveresen kialakított processzor (soft CPU), amely a RISC-V utasításkészletre épülő architektúrán alapul. A VexRiscV processzor egy 32 bites processzormegvalósítás, amely futószalag-bővítményekkel rendelkezik, és beállítható funkciókészletet kínál, így ideális az Efinix eszközökben történő megvalósításhoz. A választható beállítások közé tartozik a szorzó, az atomi utasítások, a lebegőpontos kiterjesztések és a tömörített utasítások. A teljesítmény az egylapkás rendszer beállításaitól függően 0,86 és 1,05 DMIPS/MHz között mozog.

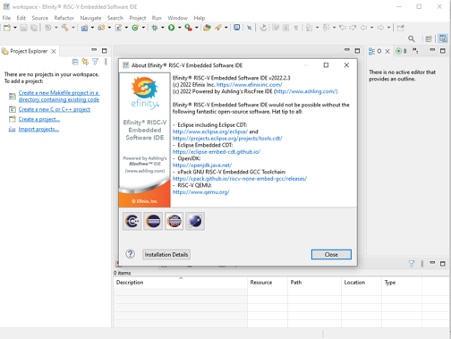

Miután a hardverkörnyezetet megtervezték, majd megvalósították az Efinix eszközben, az Ashling RiscFree IDE (integrated development environment, beépített fejlesztőkörnyezet) segítségével fejleszthető az alkalmazásszoftver. Az Ashling RiscFree egy Eclipse-alapú IDE, amely alkalmazásszoftverek létrehozására és fordítására, valamint az alkalmazás telepítés előtti finomhangolása érdekében a célponton történő hibakeresésre ad lehetőséget.

7. ábra: Az Ashling RiscFree egy Eclipse-alapú IDE, amely alkalmazásszoftverek létrehozására és fordítására, valamint a célponton történő hibakeresésére ad lehetőséget (kép: Adam Taylor)

7. ábra: Az Ashling RiscFree egy Eclipse-alapú IDE, amely alkalmazásszoftverek létrehozására és fordítására, valamint a célponton történő hibakeresésére ad lehetőséget (kép: Adam Taylor)

Beágyazott linuxos megoldás fejlesztése esetén rendelkezésre áll az összes szükséges rendszerindítási eszköz, köztük a First Stage Boot Loader (első fokozatú rendszerbetöltő), az OpenSBI, az U-Boot és a Linux rendszerépítő (buildroot). Ha valós idejű megoldásra van szükség, a fejlesztő alternatívaként használhatja a FreeRTOS operációs rendszert.

A mesterséges intelligencia megvalósítása

A mesterséges intelligencia Efinix-féle megvalósítása a szoftveresen kialakított RISC-V processzor működésére épül. Ez a megvalósítás kihasználja a RISC-V processzor egyedi utasításokkal való vezérlésének képességét, hogy lehetővé tegye a TensorFlow Lite-megoldások gyorsítását. A RISC-V processzor használata módot ad arra is, hogy a felhasználók olyan egyedi utasításokat hozzanak létre, amelyek a mesterséges intelligenciás következtetést követő elő- vagy utófeldolgozás részeként használhatók, és ezáltal egy érzékenyebb és determinisztikusabb megoldást hoznak létre.

A mesterséges intelligencia megvalósításának megkezdéséhez az első lépés az Efinix-állatkertmakett (model zoo) megismerése, amely az Efinis saját felhasználói technikájára optimalizált mesterséges intelligenciás és gépi tanulási modellek könyvtára. Az Efinix eszközökkel dolgozó fejlesztők számára elérhető az állatkertmakett, és a hálózatot a Jupyter Notebooks vagy a Google Colab segítségével lehet betanítani. A hálózat a betanítása után a TensorFlow Lite konverter segítségével lebegőpontos modellből kvantált modellé alakítható.

A TensorFlow Lite formátumba való átalakítás után az Efinix tinyML gyorsítója használható a szoftveresen kialakított RISC-V processzorra telepíthető megoldás létrehozásához. A tinyML generátor lehetővé teszi a fejlesztő számára, hogy testreszabja a gyorsító megvalósított változatát, és létrehozza a projektfájlokat. Így telepítve a gyorsulás a kiválasztott architektúrától és testreszabástól függően 4-szeres és 200-szoros közötti lehet.

Összegzés

Az Efinix eszközök egyedi XLR-architektúrájuknak köszönhetően rugalmasságot kínálnak a fejlesztőknek. Az eszközkészlet nem csak regiszterátviteli szintű (RTL, register-transfer level) tervek megvalósítására, hanem szoftveresen kialakított RISC-V processzorokat használó összetett egylapkás rendszerek megvalósítására is alkalmas. A szoftveresen kialakított egylapkás rendszerre egy mesterséges intelligenciás és gépi tanulásos megoldás épül, amely lehetővé teszi a gépi tanulásos következtetések használatát.

Disclaimer: The opinions, beliefs, and viewpoints expressed by the various authors and/or forum participants on this website do not necessarily reflect the opinions, beliefs, and viewpoints of DigiKey or official policies of DigiKey.