Nagyteljesítményű energiahatékony peremhálózati MI-alkalmazások gyors kiépítése FPGA-kkal

Contributed By DigiKey's North American Editors

2021-01-12

A mesterséges intelligenciára (MI) épülő algoritmusokat peremhálózati következtető processzorokkal megvalósítani kívánó tervezőkre folyamatos nyomás nehezedik, hogy csökkentsék az energiafogyasztást és a fejlesztési időket, még egyre növekvő feldolgozási igények ellenére is. A programozható logikai kapumátrixok (FPGA-k) különösen jó sebesség-energiahatékonyság jellemzője igen hatékony kombináció a peremhálózati mesterséges intelligenciához szükséges neurális hálózati (NN) következtetőmotorok megvalósításához. Az FPGA-kat nem ismerő fejlesztők számára azonban a hagyományos FPGA-fejlesztési módszerek bonyolultnak tűnhetnek, ami gyakran készteti őket arra, hogy kevésbé optimális megoldásokhoz forduljanak.

Ez a cikk egy egyszerűbb megközelítést ismertet a Microchip Technology-tól, amely lehetővé teszi a fejlesztők számára, hogy a hagyományos FPGA-fejlesztési módokat megkerülve FPGA-k és egy szoftverfejlesztő készlet (SDK) segítségével betanított neurális hálózatokat hozzanak létre, vagy pedig egy FPGA-alapú videókészletet használva azonnal intelligens beágyazott látórendszerek alkalmazásfejlesztésébe kezdjenek.

Miért érdemes mesterséges intelligenciát használni a peremeken?

A peremhálózati számítástechnika (edge computing) alkalmazása számos előnnyel jár a tárgyak internete (IoT) alapú rendszerek számára, olyan különböző szegmensekben, mint például az ipari automatizálás, a biztonsági rendszerek, az intelligens otthonok és más területek. Az üzemi szintet megcélzó ipari IoT (IIoT) alkalmazásokban a peremhálózati számítástechnika drámaian javíthatja a folyamatszabályozási körök válaszidejét, mivel az adatokat nem szükséges eljuttatni felhőalapú alkalmazásokhoz, majd onnan vissza, rengeteg időt takarítva meg ezzel. Hasonlóképpen, egy peremhálózati technológiára épülő biztonsági rendszer vagy egy intelligens otthoni ajtózár akkor is tovább működhet, ha a felhővel való kapcsolat akár véletlenül, akár manipuláció miatt megszakad. Sok esetben az edge computing használata ezen alkalmazások mindegyikénél segíthet csökkenteni az általános működési költségeket is azáltal, hogy csökkenti a termék felhőforrásoktól való függőségét. Ahelyett, hogy a termékeik iránti kereslet növekedése miatt váratlanul további drága felhőalapú erőforrásokra lenne szükségük, a fejlesztők a termékeikbe épített helyi feldolgozási képességekre támaszkodhatnak, és így a működési költségeket stabilan tarthatják.

A gépi tanulásra (ML) épülő következtetési modellek gyors elfogadása és ezen technológia iránti kereslet növekedése drámaian megnöveli a peremhálózati számítástechnika jelentőségét. A fejlesztők számára a következtetési modellek helyben történő feldolgozása segít csökkenteni a válaszadási késleltetést, és azokat a költségeket, amelyek a felhőalapú következtetéshez szükséges erőforrások bérlésével járnak. A felhasználók számára a helyi következtetési modellek használata növeli a bizalmat abban, hogy termékeik az internetkapcsolat időnkénti megszűnése vagy a termékgyártó felhőalapú kínálatában bekövetkező változások ellenére is működni fognak. Emellett, a biztonsággal és a magánélet védelmével kapcsolatos aggályok tovább növelhetik a helyi feldolgozás és következtetés szükségességét, hogy korlátozzák a nyilvános interneten keresztül a felhőbe továbbított érzékeny információk mennyiségét.

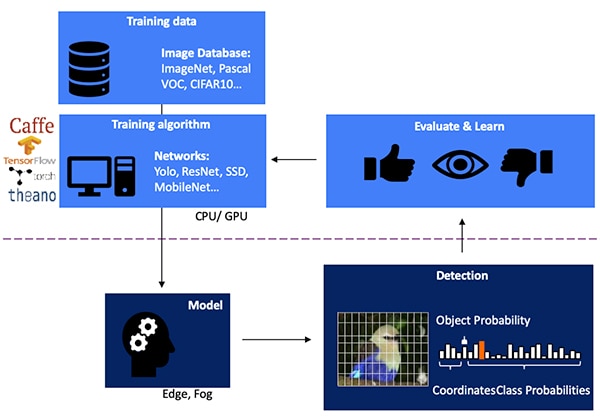

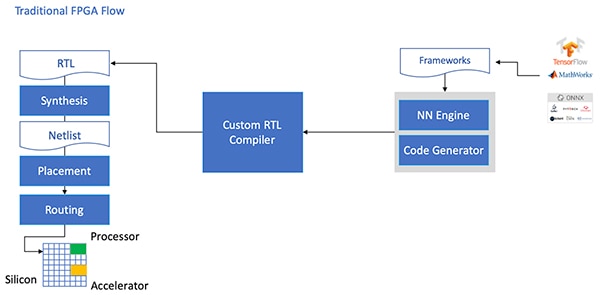

Egy látásalapú tárgyfelismeréshez alkalmas neurális hálózatra épülő következtetési modell kifejlesztése többlépcsős folyamat, amely első lépésként a modellek betanításával kezdődik, amelyet általában egy ML keretrendszerben, például a TensorFlow-ban végeznek nyilvánosan elérhető címkézett képek vagy egyedi címkézett képek felhasználásával. A feldolgozási igények miatt a modellek betanítását jellemzően grafikus feldolgozóegységekkel (GPU) végzik a felhőben, vagy más nagy teljesítményű számítási platformon. A betanítás befejezése után a modellt olyan következtetési modellé alakítják át, amely képes a peremhálózati vagy fog rétegű számítástechnikai erőforrásokon futni, és amely a következtetési eredményeket objektumosztályok valószínűségeinek halmazaként szolgáltatja (1. ábra).

1. ábra: A következtetési modell megvalósítása peremhálózati mesterséges intelligencia számára egy többlépcsős folyamat utolsó lépése, ahol a neurális hálózatoknak keretrendszerekben végrehajtott betanítására és optimalizálásra van szükség a rendelkezésre álló vagy egyedi betanítási adatok felhasználásával. (Kép: Microchip Technology)

1. ábra: A következtetési modell megvalósítása peremhálózati mesterséges intelligencia számára egy többlépcsős folyamat utolsó lépése, ahol a neurális hálózatoknak keretrendszerekben végrehajtott betanítására és optimalizálásra van szükség a rendelkezésre álló vagy egyedi betanítási adatok felhasználásával. (Kép: Microchip Technology)

Miért jelentenek számítástechnikai szempontból kihívást a következtetési modellek?

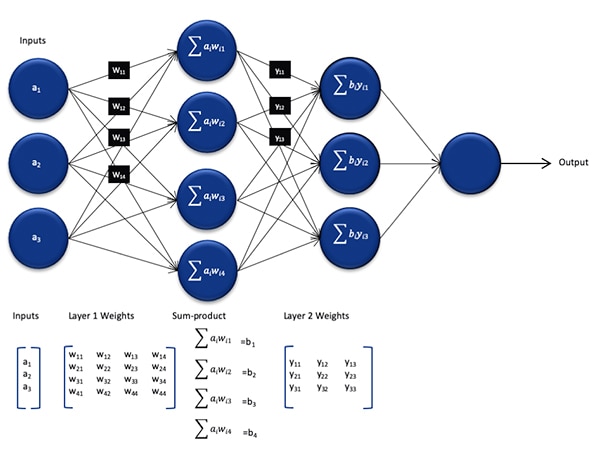

Bár a betanítási folyamat során használt modellhez képest egy neurális hálózati következtetési modell csökkentett méretű és összetettségű, még mindig számítási kihívást jelent az általános rendeltetésű processzorok számára a nagyszámú elvégzendő számítás miatt. Általános formájában egy mély neurális hálózati modell több rétegből álló neuronhalmazokból áll. A teljesen összekapcsolt hálózat minden egyes rétegén belül minden egyes nij neuronnak ki kell számítania minden egyes bemenet wij-súlyozott szorzatainak összegét (2. ábra).

2. ábra: Egy neurális hálózati alapú következtetéshez szükséges számítások száma jelentős számítási terhet jelenthet. (Kép: Microchip Technology)

2. ábra: Egy neurális hálózati alapú következtetéshez szükséges számítások száma jelentős számítási terhet jelenthet. (Kép: Microchip Technology)

A 2. ábrán nem látható az a további számítási követelmény, amelyet az aktiválási függvény támaszt, amely minden neuron kimenetét módosítja a negatív értékek nullára való leképezésével, az 1-nél nagyobb értékek 1-re való leképezésével és hasonló függvényekkel. Mindegyik nij neuron aktivációs függvényének kimenete a következő i+1 réteg bemeneti függvénye, és ez így folytatódik minden egyes réteg esetében. A neurális hálózat kimeneti rétegének végeredménye egy kimeneti vektor, amely azt a valószínűséget képviseli, hogy az eredeti bemeneti vektor (vagy mátrix) milyen mértékben felel meg a felügyelt tanulási folyamat során használt osztályok (vagy címkék) egyikének.

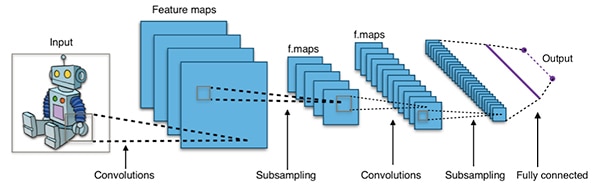

Hatékony neurális hálózati modellek hozhatók létre, amelyek a fent bemutatott reprezentatív általános neurális hálónál sokkal nagyobb és összetettebb architektúrákra épülnek. Például egy képi objektumok felismerésére használt tipikus konvolúciós neurális hálózat (CNN) darabonként alkalmazza ezeket az elveket, vagyis egy bemeneti kép szélességét, magasságát és színmélységét vizsgálja, hogy létrehozzon egy sor olyan tulajdonságtérképet, amelyekből végül összeáll a kimeneti előrejelzési vektor (3. ábra).

3. ábra: A képi tárgyfelismeréshez használt CNN hálózatok nagyszámú neuront tartalmaznak sok rétegben, ami nagyobb igényeket támaszt a számítási platformmal szemben. (Kép: Aphex34 CC BY-SA 4.0)

3. ábra: A képi tárgyfelismeréshez használt CNN hálózatok nagyszámú neuront tartalmaznak sok rétegben, ami nagyobb igényeket támaszt a számítási platformmal szemben. (Kép: Aphex34 CC BY-SA 4.0)

FPGA-k használata a neurális hálózatokon belüli számítások felgyorsítására

Bár a következtetési modellek peremhálózati helyszíneken történő végrehajtására továbbra is számos lehetőség kínálkozik, kevés olyan alternatíva van, amely optimálisan ötvözné a rugalmasságot, a számítási teljesítményt és az energiahatékonyságot, amelyre a gyakorlatban a nagysebességű következtetéseknek a peremeken történő kivitelezéséhez szükséges. A peremhálózati mesterséges intelligencia esetében könnyen megvalósítható alternatívák közül az FPGA-k különösen hatékonyak, mivel a számításigényes műveletekhez viszonylag kis energiafogyasztás mellett képesek nagy teljesítményű hardveralapú végrehajtást biztosítani.

Előnyeik ellenére az FPGA-kat néha mellőzik a hagyományos fejlesztési folyamat miatt, ami ijesztő lehet a széleskörű FPGA-tapasztalattal nem rendelkező fejlesztők számára. Egy NN-keretrendszer által generált NN-modellnek FPGA-val történő hatékony megvalósításához a fejlesztőnek az optimális megvalósítás érdekében részletekbe menően ismernie kell a modell regiszterátviteli nyelvre (RTL) való átalakítását, a terv szintézisének elkészítését és a végső fizikai tervezési szakasznál az alkatrészek és útvonalak elhelyezését (4. ábra).

4. ábra: Egy NN-modell FPGA-n történő megvalósításához a fejlesztőknek eddig tudniuk kellett, hogyan kell a modelljüket RTL-be konvertálni, majd végigmenni a hagyományos FPGA-fejlesztő folyamaton. (Kép: Microchip Technology)

4. ábra: Egy NN-modell FPGA-n történő megvalósításához a fejlesztőknek eddig tudniuk kellett, hogyan kell a modelljüket RTL-be konvertálni, majd végigmenni a hagyományos FPGA-fejlesztő folyamaton. (Kép: Microchip Technology)

A Microchip Technology a PolarFire FPGA-ival, a speciális szoftverével és a kapcsolódó szellemi termékekkel (intellectual propery, IP) olyan megoldást kínál, amely a peremeken történő nagy teljesítményű, alacsony energiafelhasználású következtetést széles körben elérhetővé teszi az FPGA-tapasztalattal nem rendelkező fejlesztők számára is.

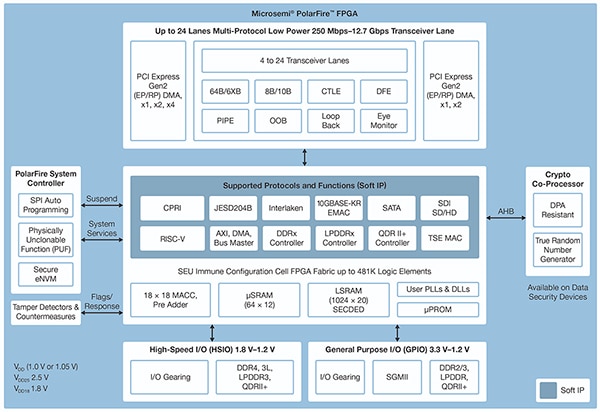

A PolarFire FPGA-kat korszerű, nem illékony technológiával gyártják, és úgy tervezték őket, hogy maximalizálják a rugalmasságot és a teljesítményt, az energiafogyasztás minimalizálása mellett. A kommunikációs és bemeneti/kimeneti (I/O) nagysebességű interfészek széles skálája mellett mély FPGA-szerkezeti összekötő hálózattal rendelkeznek, amely soft IP-magok segítségével, beleértve a RISC-V processzorokat, a korszerű memóriavezérlőket és más szabványos interfész alrendszereket képes támogatni a korszerű funkciókat (5. ábra).

5. ábra: A Microchip Technology PolarFire architektúra olyan mély összeköttetési hierarchiát biztosít, amelyet a nagy teljesítményű tervezési követelmények támogatására terveztek, beleértve a számításigényes következtetési modellek megvalósítását is. (Kép: Microchip Technology)

5. ábra: A Microchip Technology PolarFire architektúra olyan mély összeköttetési hierarchiát biztosít, amelyet a nagy teljesítményű tervezési követelmények támogatására terveztek, beleértve a számításigényes következtetési modellek megvalósítását is. (Kép: Microchip Technology)

A PolarFire FPGA-k összeköttetési hierarchiája különböző széleskörű logikai elemeket és speciális blokkokat tartalmaz, amelyeket a PolarFire FPGA család tagjai, köztük az MPF100T, MPF200T, MPF300T és MPF500T sorozat különböző mértékben támogatnak (1. táblázat).

|

1. táblázat: A PolarFire sorozatban számos különböző tulajdonságokkal rendelkező és kapacitású FPGA-struktúra áll rendelkezésre. (Táblázat: DigiKey, a Microchip Technology PolarFire adatlapja alapján)

A következtetés gyorsítása szempontjából különösen érdekes funkciók közül a PolarFire architektúra tartalmaz egy dedikált matematikai blokkot, amely egy 18 × 18 bites előjeles szorzó-összeadó függvényt (MAC) biztosít, előösszeadóval. A beépített skalárszorzat üzemmód egyetlen matematikai blokkot használ két 8 bites szorzási művelet elvégzésére, ami a modell kvantálását követően a pontosságra gyakorolt elhanyagolható hatás kihasználásával növeli a számítási kapacitást.

A matematikai műveletek felgyorsítása mellett a PolarFire architektúra segít enyhíteni a következtetési modellek általános célú architektúrákon történő megvalósítása során felmerülő memóriatúlterhelést, például az NN-algoritmus végrehajtása során létrehozott köztes eredményeknek a kis elosztott memóriákon való tárolásakor. Az NN-modell súlyfüggvényei és torzítási értékei a matematikai blokk közelében található logikai elemekből felépített 16 mélységű, 18 bites együtthatójú, csak olvasható memóriában (ROM) is tárolhatók.

A PolarFire FPGA struktúra egyéb funkcióival kombinálva a matematikai blokkok a Microchip Technology magasabb szintű CoreVectorBlox nevű szellemi termékének (IP-jének) alapját képezik. Ez egy rugalmas NN-motor feladatát látja el, amely képes különböző típusú NN-ek végrehajtására. A CoreVectorBlox IP egy sor vezérlőregiszter mellett három fő funkcionális blokkot tartalmaz:

- Mikrovezérlő: egy egyszerű RISC-V soft processzor, amely a Microchip firmware bináris nagy objektumát (BLOB) és a felhasználó egyedi NN BLOB fájlját olvassa be külső tárolóból. A firmware BLOB-ból származó utasítások végrehajtásával vezérli a CoreVectorBlox általános műveleteit.

- Mátrixprocesszor (MXP): nyolc 32 bites aritmetikai logikai egységből (ALU) álló soft processzor, amelyet úgy terveztek, hogy párhuzamos műveleteket végezzen adatvektorokon elemi tenzorműveletekkel, beleértve az add, sub, xor, shift, mul, dotprod és egyéb műveleteket, szükség szerint 8, 16 és 32 bites vegyes pontossággal.

- CNN gyorsító: az MXP műveleteket egy kétdimenziós MAC-függvénytömb segítségével gyorsítja fel, amely matematikai blokkokkal van megvalósítva és 8 bites pontossággal működik.

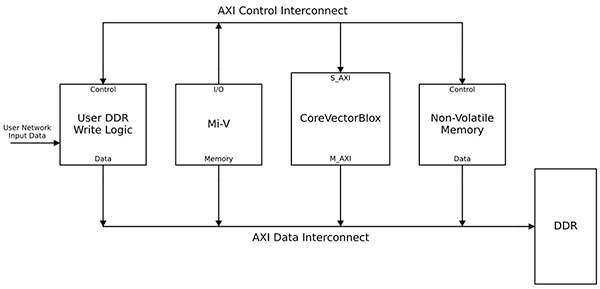

Egy komplett NN-feldolgozó rendszer egy CoreVectorBlox IP-blokk, memória, memóriavezérlő és egy gazdaprocesszor, például a Microsoft RISC-V (Mi-V) szoftveres processzormag kombinációjából áll (6. ábra).

6. ábra: A CoreVectorBlox IP-blokk egy neurális hálózat alapú következtetési modell megvalósítása érdekében együttműködik egy gazdaprocesszorral, például a Microchip Mi-V RISC-V mikrokontrollerével. (Kép: Microchip Technology)

6. ábra: A CoreVectorBlox IP-blokk egy neurális hálózat alapú következtetési modell megvalósítása érdekében együttműködik egy gazdaprocesszorral, például a Microchip Mi-V RISC-V mikrokontrollerével. (Kép: Microchip Technology)

Egy videorendszeres megvalósításban a gazdaprocesszor a firmware- és hálózati BLOB-okat a rendszer flashmemóriájából tölti be, és a CoreVectorBlox blokk általi használatra a kétszeres átviteli sebességű (DDR) típusú véletlen hozzáférésű memóriába (RAM) másolja őket. Ahogy a videoképek megérkeznek, a gazdaprocesszor a DDR RAM-ba írja őket, és jelzi a CoreVectorBlox blokknak, hogy kezdje meg a kép feldolgozását. Miután lefuttatta a hálózati BLOB-ban meghatározott következtetési modellt, a CoreVectorBlox blokk beírja az eredményeket, beleértve a képre adott osztályozást is a DDR RAM-ba, hogy a célalkalmazás fel tudja azt használni.

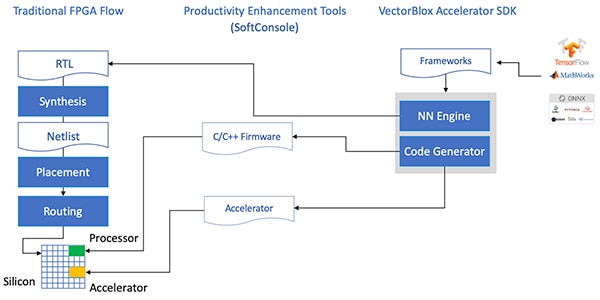

A fejlesztési folyamatnak köszönhetően az FPGA alapú neurális hálózati rendszerek egyszerűbben megvalósíthatók

A PolarFire esetében a Microchip megóvja a fejlesztőket attól a komplexitástól, amely egyébként általában az NN-következtetési modelleknek FPGA-kon történő megvalósításával jár. A hagyományos FPGA-fejlesztési folyamattal való részletekbe menő foglalkozás helyett az NN-modellek fejlesztői a szokásos módon dolgoznak a saját NN-keretrendszereiken belül, és az így kapott modellt betöltik a Microchip Technology VectorBlox Accelerator Software Development Kit (SDK) szoftverfejlesztő készletébe. Az SDK létrehozza a szükséges fájlokat, beleértve a normál FPGA-fejlesztési folyamathoz szükséges fájlokat, valamint a korábban említett firmware- és hálózati BLOB-fájlokat is (7. ábra).

7. ábra: A VectorBlox Accelerator SDK kezeli az NN-modell FPGA-n történő megvalósításának részleteit, automatikusan generálva az FPGA-alapú következtetési modell tervezéséhez és futtatásához szükséges fájlokat. (Kép: Microchip Technology)

7. ábra: A VectorBlox Accelerator SDK kezeli az NN-modell FPGA-n történő megvalósításának részleteit, automatikusan generálva az FPGA-alapú következtetési modell tervezéséhez és futtatásához szükséges fájlokat. (Kép: Microchip Technology)

Mivel a VectorBlox Accelerator SDK-val történő munkafolyamat esetén az NN-terv az FPGA-ba implementált NN-motorra töltődik rá, különböző NN-ek futtathatók ugyanazon az FPGA-terven anélkül, hogy újra kellene végezni az FPGA-terv szintézisét. A fejlesztők C/C++ kódot készítenek az így létrejövő rendszerhez, és a rendszeren belül képesek menet közben váltani a modelleket, vagy azokat időszeletelés segítségével egyszerre futtatni.

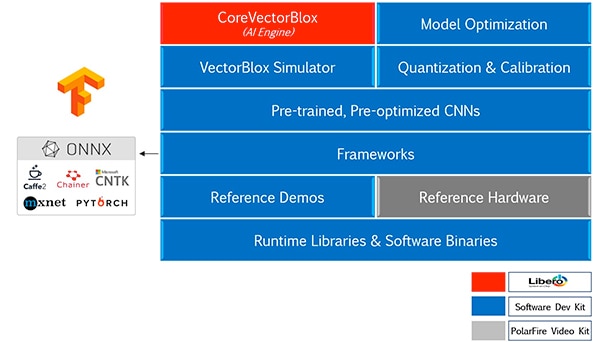

A VectorBlox Accelerator SDK a Microchip Technology Libero FPGA tervezőcsomagját bővíti ki az NN-következtetési modellek fejlesztéséhez szükséges átfogó lehetőségekkel. A modelloptimalizálási, kvantálási és kalibrációs funkciók mellett az SDK egy NN-szimulátort is biztosít, amely egy kapott BLOB-fájl felhasználásával lehetővé teszi a fejlesztők számára a modelljük kiértékelését, mielőtt a fájlt az FPGA hardveres megvalósításban használnák (8. ábra).

8. ábra: A VectorBlox Accelerator SDK átfogó szolgáltatáscsomagot kínál a keretrendszerek által generált következtetési modellek FPGA-kra történő implementációjának optimalizálására. (Kép: Microchip Technology)

8. ábra: A VectorBlox Accelerator SDK átfogó szolgáltatáscsomagot kínál a keretrendszerek által generált következtetési modellek FPGA-kra történő implementációjának optimalizálására. (Kép: Microchip Technology)

A VectorBlox Accelerator SDK támogatja az Open Neural Network Exchange (ONNX) formátumú modelleket, valamint számos más keretrendszerből, köztük a TensorFlow, a Caffe, a Chainer, a PyTorch, a MXNET és más fejlesztőkörnyezetekből származó modelleket is. A támogatott CNN-architektúrák között megtalálható az MNIST, különböző MobileNet verziók, a ResNet-50, a Tiny Yolo V2 és a Tiny Yolo V3. A Microchip azon dolgozik, hogy a támogatást kiterjessze a nyílt forráskódú OpenVINO eszközkészlet előre betanított modelleket tartalmazó nyílt modellkészletének legtöbb hálózatára is, többek között a Yolo V3, Yolo V4, RetinaNet és SSD-MobileNet modellekre.

Az FPGA-val megvalósított következtetést bemutató videokészlet

Annak érdekében, hogy a fejlesztők gyorsan belevághassanak az intelligens beágyazott képalkotó alkalmazások fejlesztésébe, a Microchip Technology kínálatában szerepel egy átfogó mintaalkalmazás és referenciaterv, amelyet a vállalat MPF300-VIDEO-KIT jelű PolarFire FPGA alapú video- és képalkotó készleten való futtatásra terveztek.

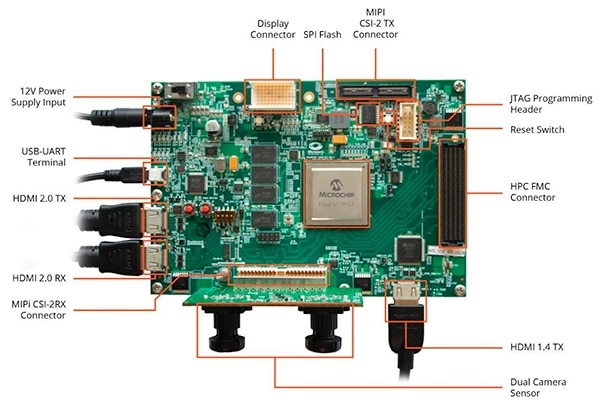

A Microchip MPF300T PolarFire FPGA-ra épülő készlet áramköri lapja két kameraérzékelő, DDR4 típusú RAM, flashmemória, energiagazdálkodási elemek és különféle interfészek kombinációját tartalmazza (9. ábra).

9. ábra: Az MPF300-VIDEO-KIT PolarFire FPGA video- és képalkotó készlet és a hozzá tartozó szoftver a fejlesztők számára gyors kezdési lehetőséget biztosít az FPGA-alapú következtetés megvalósítására intelligens beágyazott látórendszeri alkalmazásokban. (Kép: Microchip Technology)

9. ábra: Az MPF300-VIDEO-KIT PolarFire FPGA video- és képalkotó készlet és a hozzá tartozó szoftver a fejlesztők számára gyors kezdési lehetőséget biztosít az FPGA-alapú következtetés megvalósítására intelligens beágyazott látórendszeri alkalmazásokban. (Kép: Microchip Technology)

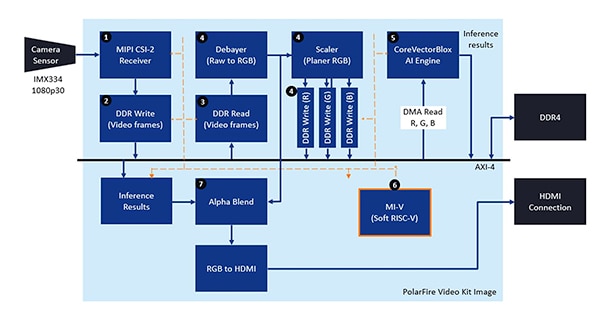

A készlet tartalmaz egy teljes Libero környezetben fejlesztett projektet, amely a firmware és a hálózati BLOB fájlok létrehozására szolgál. A BLOB-fájloknak az áramköri lapon lévő flashmemóriába programozása után, a fejlesztők a Libero-ban lévő futtatás gombra kattintva elindítják a demonstrációt, amely feldolgozza a kamera érzékelőjétől érkező videoképeket, és megjeleníti a következtetések eredményeit egy kijelzőn (10. ábra).

10. ábra: A Microchip Technology PolarFire FPGA video- és képalkotó készlete bemutatja egy intelligens beágyazott látórendszer FPGA-val történtő megvalósítását és tervezését, amely a Microchip CoreVectorBlox NN-motorjára épül. (Kép: Microchip Technology)

10. ábra: A Microchip Technology PolarFire FPGA video- és képalkotó készlete bemutatja egy intelligens beágyazott látórendszer FPGA-val történtő megvalósítását és tervezését, amely a Microchip CoreVectorBlox NN-motorjára épül. (Kép: Microchip Technology)

Az FPGA-alapú rendszer minden egyes bemeneti videóképkocka esetében a következő lépéseket hajtja végre (ahol a lépések számai a 10. ábrának megfelelőek):

- Képkocka betöltése a kamerából

- A keret tárolása a RAM-ban

- A keret beolvasása a RAM-ból

- A nyers kép konvertálása RGB-be, planer RGB-be, és az eredmény tárolása a RAM-ban

- Az Mi-V soft RISC-V processzor elindítja a CoreVectorBlox motort, amely lekérdezi a képet a RAM-ból, végrehajtja a következtetést, és az osztályozásból kapott valószínűségi eredményeket beírja a RAM-ba

- Az Mi-V az eredmények alapján egy átfedési keretet hoz létre határoló dobozokkal, osztályozási eredményekkel és egyéb metaadatokkal, és a keretet a RAM-ban tárolja

- Az eredeti képkocka keveredik az átfedő képkockával, és megjelenítődik a HDMI-kijelzőn

A bemutató készlet támogatja a Tiny Yolo V3 és a MobileNet V2 modellek gyorsítását, de a fejlesztők más SDK által támogatott modelleket is futtathatnak a korábban ismertetett módszerekkel úgy, hogy a modell nevének és metaadatainak a két alapértelmezett modellt tartalmazó meglévő listához való hozzáadásával módosítják kissé a kódot.

Összegzés

A mesterséges intelligenciára épülő algoritmusok, mint például a neurális hálózati modellek jellemzően olyan számításigényes munkaterhelést jelentenek, amely az általános célú processzoroknál jóval erősebb számítási erőforrásokat igényel. Bár az FPGA-k jól felszereltek arra, hogy megfeleljenek a következtetési modellek futtatásához szükséges teljesítmény- és energiatakarékossági követelményeknek, a hagyományos FPGA-fejlesztési módszerek bonyolultnak tűnhetnek, ami gyakran arra készteti a fejlesztőket, hogy nem optimális megoldásokhoz folyamodjanak.

Mint bemutattuk, a Microchip Technology speciális szellemi terméke (IP-je) és szoftvere segítségével az FPGA-tapasztalattal nem rendelkező fejlesztők is megvalósíthatják a következtetésre épülő terveket, amelyek jobban megfelelnek a teljesítményre, az energiafogyasztásra és a tervezési ütemezésre vonatkozó követelményeknek.

Disclaimer: The opinions, beliefs, and viewpoints expressed by the various authors and/or forum participants on this website do not necessarily reflect the opinions, beliefs, and viewpoints of DigiKey or official policies of DigiKey.