A társprocesszoros architektúra: egy beágyazott rendszerarchitektúra gyors prototípuskészítéshez

2021-07-06

A szerkesztő megjegyzése – Bár a társprocesszoros architektúra jól ismert a digitális feldolgozási teljesítményéről és áteresztőképességéről, a beágyazott rendszerek tervezői számára lehetőséget nyújt olyan projektmenedzsment-stratégiák megvalósítására, amelyek javítják mind a fejlesztési költségeket, mind a piacra kerülési időt. Ez a cikk, amely kifejezetten egy diszkrét mikrovezérlő (MCU) és egy diszkrét programozható logikai kapumátrix (FPGA) kombinációjára összpontosít, bemutatja, hogy ez az architektúra hogyan teszi lehetővé a hatékony és iteratív tervezési folyamatot. A kutatott források, empirikus eredmények és esettanulmányok felhasználásával feltárja ennek az architektúrának az előnyeit, és példa alkalmazásokat mutat be. A cikk végén a beágyazott rendszerek tervezői jobban megérthetik, mikor és hogyan érdemes ezt a sokoldalú hardverarchitektúrát alkalmazni.

Bevezetés

Egy-egy munka megkezdésekor a beágyazott rendszerek tervezői a tervezési korlátok, a teljesítménybeli elvárások, valamint az ütemtervvel és költségvetéssel kapcsolatos szempontok által képezett korlátok között találják magukat. Valójában még a modern projektmenedzsmentben használt szavakban és kifejezésekben rejlő ellentmondások is alátámasztják e szerepkör bizonytalan és ideiglenes jellegét: „bukj gyorsan”; „legyél agilis”; „tervezd jövőbiztosra”; és „rombold le a berögzült hagyományokat!". Már az is egy pokoli akrobatamunka, ha csupán megpróbálkozunk ezen elvárások kielégítésével, és mégis, ezek az elvárások hallhatók és egyre csak erősödnek az egész piacon. Olyan tervezési megközelítésre van szükség, amely lehetővé teszi evolúciós, iteratív folyamatok megvalósítását, és ahogy a legtöbb beágyazott rendszer esetében, ez is a hardverarchitektúrával kezdődik.

A társprocesszoros architektúra, egy olyan hardverarchitektúra, amely arról ismert, hogy egyesíti a mikrovezérlő egységek (MCU) és az FPGA-k (Field Programmable Gate Array) erősségeit, és olyan eljárást kínál a beágyazott rendszerek tervezőinek, amely képes megfelelni a legigényesebb követelményeknek is, ugyanakkor megfelelően rugalmas ahhoz, hogy az ismert és az ismeretlen problémák is kezelhetők legyenek. Az iteratív alkalmazkodásra képes hardver biztosításával a tervező demonstrálhatja a fejlődést, elérheti a kritikus mérföldköveket, és teljes mértékben kihasználhatja a gyors prototípuskészítési folyamat előnyeit.

Ezen a folyamaton belül kulcsfontosságú projektfejlesztési mérföldkövek találhatók, amelyek mindegyike egyedileg járul hozzá a fejlesztés egészéhez. Ebben a cikkben ezeket a mérföldköveket a következő elnevezésekkel illetjük: a „Digitális jelfeldolgozás a mikrovezérlővel” mérföldkő, a „Rendszer irányítása a mikrovezérlővel” mérföldkő és a „Termékbevezetés” mérföldkő.

A cikk végére bizonyítást nyer, hogy a rugalmas hardverarchitektúrák alkalmazása jobban megfelel a modern beágyazott rendszerek tervezésére, mint a merevebb megközelítések. Ez a megközelítés továbbá a projektköltségek és a piacra jutási idő tekintetében is javulást eredményezhet. Ezen álláspontot érvekkel, példákkal és esettanulmányokkal támasztjuk alá. Ha az ilyen architektúrák által biztosított tervezési rugalmasságot illetően megvizsgáljuk az egyes mérföldkövek elérése által képviselt értéket, világossá válik, hogy az adaptív hardverarchitektúrák erőteljesen előre tudják mozdítani a beágyazott rendszerek kifejlesztését.

A társprocesszoros architektúra erősségei: tervezési rugalmasság és nagy teljesítményű feldolgozás

Az FPGA-kialakításokat gyakran használják arra, hogy közvetlenül kapcsolódjanak nagy sebességű analóg-digitális átalakítókhoz (ADC). A jelet digitalizálják, beolvassák az FPGA-ba, majd néhány digitális jelfeldolgozó (DSP) algoritmus futtatásával feldolgozzák. Végül, az FPGA döntéseket hoz a kapott eredmények alapján.

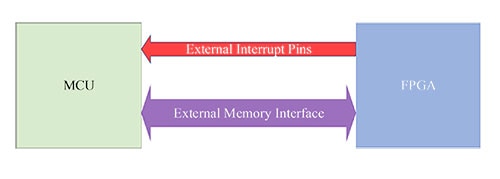

Egy ilyen alkalmazás szolgál majd példaként ebben a cikkben. Az 1. ábra továbbá egy általános társprocesszoros architektúrát mutat be, ahol az MCU és az FPGA az MCU külső memóriainterfészén keresztül kapcsolódnak egymáshoz. Az FPGA-val úgy bánnak, mintha egy külső statikus közvetlen hozzáférésű memória (SRAM) lenne. A jelek az FPGA-ból érkeznek vissza az MCU-hoz, és hardveres megszakítási vonalakként és állapotjelzőkként szolgálnak. Ez lehetővé teszi az FPGA számára, hogy jelezze a kritikus állapotokat az MCU-nak, például azt, hogy kész van egy ADC konverzióval, illetve hiba, vagy más figyelemre méltó esemény történt.

1. ábra: Általános társprocesszor blokk vázlata (MCU + FPGA). (Forrás: CEPD)

1. ábra: Általános társprocesszor blokk vázlata (MCU + FPGA). (Forrás: CEPD)

A társprocesszoros megközelítés erősségei valószínűleg a fent említett mérföldkövek eredményeiben mutatkoznak meg a legjobban. Az értéket nem csak egy-egy feladat vagy fázis teljesítésének feltüntetésével, hanem az ezen eredmények által lehetővé tett új lehetőségek felmérésével is értékeljük. Az alábbi kérdésekre adott válaszok segítenek felmérni, hogy egy-egy mérföldkő elérésének általánosan nézve mekkora értéke van:

- A többi munkatárs most már gyorsabban tud előrehaladni, mivel a projektfüggőségek és más akadályok megszűnnek?

- A mérdföldkő elérésével elért eredményeknek köszöhetően milyen újabb további párhuzamos fejlesztési utak válnak lehetővé?

A „Digitális jelfeldolgozás a mikrovezérlővel” mérföldkő

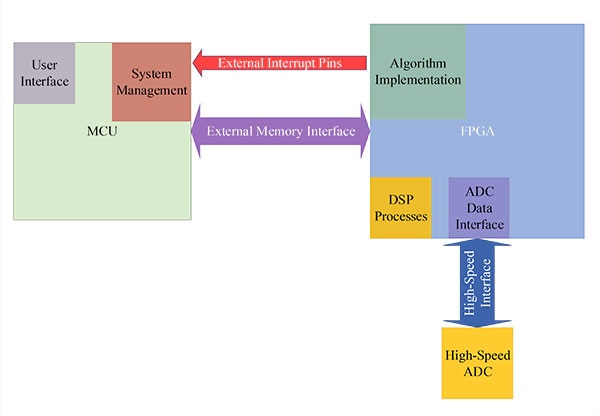

2. ábra: Architektúra - digitális jelfeldolgozás a mikrovezérlővel. (Kép: CEPD)

2. ábra: Architektúra - digitális jelfeldolgozás a mikrovezérlővel. (Kép: CEPD)

Az első fejlesztési szakasz, amely lehetővé válik ezzel a hardverarchitektúrával a középpontba helyezi az MCU-t. Mindent egybevetve, az MCU és a futtatható szoftverek fejlesztése kevesebb erőforrást és időt igényel, mint az FPGA és a hardverleíró nyelv (HDL) fejlesztése. Így azáltal, hogy a termékfejlesztés úgy kezdődik, hogy az MCU az elsődleges processzor, az algoritmusok gyorsabban megvalósíthatók, tesztelhetők és validálhatók. Ez már a tervezési folyamat korai szakaszában lehetővé teszi az algoritmusban lévő és a logikai hibák felfedezését, valamint a jellánc jelentős részeinek tesztelését és validálását.

Az FPGA szerepe ennél a kezdeti mérföldkőnél az, hogy nagy sebességű adatgyűjtő interfészként viselkedjen. Feladata, hogy megbízhatóan továbbítsa a nagysebességű ADC által küldött adatokat, figyelmeztesse az MCU-t, hogy az adatok rendelkezésre állnak, és eljuttassa ezeket az adatokat az MCU külső memóriainterfészére. Bár ez a szerep nem foglalja magában a HDL-alapú DSP-folyamatok vagy más algoritmusok megvalósítását, mégis rendkívül fontos.

Az ebben a fázisban végzett FPGA-fejlesztés megalapozza a termék végső sikerét mind a termékfejlesztési erőfeszítések során, mind a piacra kerüléskor. A csak az alacsony szintű interfészre való összpontosítással, elegendő idő fordítható ezeknek az alapvető műveleteknek a tesztelésére. Csak akkor lehet magabiztosan kimondani, hogy a projekt sikeresen elért ehhez a mérföldkőhöz, ha az FPGA megbízhatóan és magabiztosan teljesít ebben az összekötő szerepben.

E kezdeti mérföldkő elérésének legfontosabb eredményei a következő előnyöket foglalják magukban:

- A teljes jelút – minden erősítés, csillapítás és átalakítás – tesztelése és validálása megtörtént.

- A projekt fejlesztési ideje és a ráfordítások csökkentek azáltal, hogy az algoritmusokat kezdetben szoftveresen (C/C++) valósították meg. Ennek igen nagy jelentősége van a vezetőség és más érdekelt felek számára, akiknek a termékfejlesztés elkövetkező fázisainak jóváhagyása előtt meg kell győződniük a projekt megvalósíthatóságáról.

- Az algoritmusok C/C++ nyelvben történő megvalósításából levont tanulságok közvetlenül átvihetők a HDL implementációkra – a szoftverből HDL-be átültető eszközök, pl. a Xilinx HLS segítségével.

A „Rendszer irányítása a mikrovezérlővel” mérföldkő

3. ábra: Architektúra - a rendszer irányítása a mikrovezérlővel. (Kép: CEPD)

3. ábra: Architektúra - a rendszer irányítása a mikrovezérlővel. (Kép: CEPD)

A második fejlesztési szakasz ilyen társprocesszoros megközelítés esetén az, hogy a DSP-folyamatok és az algoritmusok implementálása az MCU-ból áthelyeződik az FPGA-ba. Az FPGA továbbra is végzi a nagysebességű ADC interfész irányítását, azonban azáltal, hogy átveszi ezeket a további szerepeket is, az FPGA képessége, vagyis az általa nyújtott sebesség és párhuzamosság teljes mértékben kihasználható. Továbbá, az MCU-tól eltérően, egyidejűleg több DSP-folyamat és algoritmus csatorna is megvalósítható és futtatható.

Az MCU-val implementált megoldás tanulságaira alapozva a tervező ezt a korrekt működést viszi tovább a következő szakaszba. Az olyan eszközök, mint a fent említett Vivado HLS a Xilinx-től, a futtatható C/C++ kódot működőképes szintetizálható HDL-be fordítják. Az időzítési korlátokat, folyamatparamétereket és egyéb felhasználói preferenciákat még mindig meg kell határozni és implementálni kell, az alapvető funkcionalitás azonban megmarad és átkerül az FPGA-struktúrára.

Ennél a mérföldkőnél az MCU a rendszerirányító szerepét látja el. Az FPGA-n belüli állapot- és vezérlőregisztereket az MCU figyeli, frissíti és állapotukat jelenti. Ezenkívül az MCU kezeli a felhasználói felületet (UI) is. Ez a felhasználói felület lehet egy Ethernet vagy Wi-Fi kapcsolaton keresztül elérhető webszerver, vagy pedig lehet egy ipari érintőképernyős felület, amely a felhasználók számára helyszíni hozzáférést biztosít. Az MCU új, kifinomultabb szerepéből levonható legfontosabb tanulság a következő: azáltal, hogy az MCU-t és az FPGA-t tehermentesítették a számításigényes feldolgozási feladatok végzése alól, mind az MCU-t, mind az FPGA-t olyan feladatokra tudják kihasználni, amelyekre azok jól alkalmasak.

E mérföldkő elérésének legfontosabb eredményei a következő előnyöket foglalják magukban:

- A DSP-folyamatok és algoritmusok gyors, párhuzamos végrehajtását az FPGA biztosítja.Az MCU jól kezelhető és letisztult felhasználói felületet biztosít, és végzi a termék folyamatainak irányítását.

- Mivel az algoritmusokat az MCU-n belül már kifejlesztették és validálták, az algoritmusbeli hibalehetőségeket ezzel csökkentették, és ezeket szintetizálható HDL-be is átültették. Speciális eszközök, mint például a Vivado HLS, megkönnyítik ezt az átültetési folyamatot. Továbbá, az FPGA-ra jellemző specifikus kockázatok az integrált szimulációs eszközökkel, például a Vivado tervezőcsomaggal csökkenthetők.

- A termékfejlesztésben érdekelt felek számára nem jár jelentős kockázattal az, hogy a folyamatokat az FPGA-ra helyezik át. Éppen ellenkezőleg, láthatják és örülhetnek az FPGA által kínált sebesség és párhuzamosság előnyeinek. Mérhető működésbeli javulás figyelhető meg, és most már összpontosítani lehet a tervnek a gyártásra való előkészítésére.

A termékbevezetési mérföldkő

Mivel a számításigényes feldolgozást elvégzi az FPGA, az MCU pedig ellátja a rendszerirányítási és a felhasználói felület kezelésével kapcsolatos feladatokat, a termék készen áll a bevezetésre. Ez az írás nem érvel amellett, hogy meg kellene kerülni az alfa és béta verziók kiadását, e mérföldkőt illetően azonban a hangsúly azokon a lehetőségeken van, amelyeket a társprocesszoros architektúra a termékbevezetés tekintetében biztosít.

Mind az MCU, mind az FPGA olyan eszközök, amelyek a terepen programozhatók. Számos előrelépés történt annak érdekében, hogy az FPGA terepi programozása ugyanolyan elérhető legyen, mint a szoftverfrissítések. Továbbá, mivel az FPGA az MCU címezhető memóriaterületén belül van, az MCU szolgálhat az egész rendszer hozzáférési pontjaként: képes egyaránt fogadni mind a saját, mind az FPGA frissítéseit. A frissítések minden végfelhasználóra vonatkozólag feltételesen ütemezhetők, terjeszthetők és testre szabhatók. Végezetül, a felhasználói és használati naplók fenntarthatók és az egyes megvalósításokhoz társíthatók. Ezekből az adatkészletekből a működés tovább finomítható és javítható, még azután is, hogy a termék már a terepen van.

A teljes rendszer frissíthetőségével járó előnyöket talán semmi sem támasztja alá jobban, mint a világűrbe telepített alkalmazások. A termék bevezetése után annak működésének fenntartását és frissítését távolról kell végezni. Ez állhat csupán a logikai feltételek egyszerű megváltoztatásából, de lehet olyan bonyolult is, mint egy kommunikációs modulációs séma frissítése. Az FPGA-technológiák által kínált programozhatóság és a társprocesszoros architektúra ezen lehetőségeket biztosítja a teljes lehetséges skálán keresztül, miközben sugárzásálló alkatrészeket kínál.

Az ezen mérföldkőből levonható utolsó fontos tanulság a költségek fokozatos csökkenése. Költségcsökkentések, az anyagjegyzék (BOM) módosítása és egyéb optimalizálás is történhet ennél a mérföldkőnél. A terepi telepítések során kiderülhet, hogy a termék ugyanolyan jól tud működni egy olcsóbb MCU-val vagy egy kevésbé erős FPGA-val is. A társprocesszornak köszönhetően az architektúra tervezői nem kényszerülnek olyan komponensek használatára, amelyek a képességeiket tekintve sokkal erősebbek, mint amire egy adott alkalmazás esetén szükség van. Továbbá, ha egy alkatrész gyártása esetleg megszűnne, az architektúra lehetővé teszi, hogy a kialakításba egy új komponens kerüljön. Az egychipes és a system on a chip (SoC) architektúrák esetén nem ez a helyzet, illetve egy termék összes folyamatait irányító nagy teljesítményű DSP vagy MCU esetében sem. A társprocesszoros architektúra jól ötvözi a képességeket és a rugalmasságot, amely a tervezők számára mind a fejlesztési fázisokban, mind a piacra kerüléskor több választási lehetőséget és szabadságot biztosít.

Alátámasztó kutatások és kapcsolódó esettanulmányok

Műholdas kommunikációs példa

Röviden, a társprocesszor értéke abban rejlik, hogy tehermentesíteni tudja az elsődleges feldolgozóegységet, így a feladatok végrehajtása hardveresen történik, ahol a gyorsítások és az egyszerűsítések előnyei kihasználhatók. Egy ilyen kialakítás mellett való döntés előnye a számítási sebesség és a képességek általános növekedése, valamint – ahogyan ez a cikk is állítja – a fejlesztési költségek és a fejlesztési idő csökkenése. Talán az egyik legmeggyőzőbb terület, ahol ezek az előnyök érvényesülnek az űrbeli kommunikációs rendszerek.

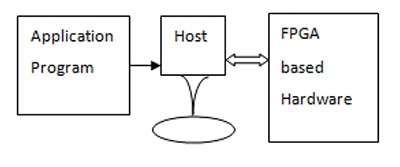

G. Prasad és N. Vasantha az FPGA based hardware as coprocessor című kiadványukban részletesen bemutatják, hogy egy FPGA-n belüli adatfeldolgozás hogyan vegyíti a műholdas kommunikációs rendszerek számítási igényeit anélkül, hogy az alkalmazásspecifikus integrált áramkörök (ASIC) magas egyszeri mérnöki költségei vagy a merev architektúrájú processzorok alkalmazásspecifikus korlátai felmerülnének. A Digitális jelfeldolgozás a mikrovezérlővel című mérföldkőnél leírtakhoz hasonlóan a tervezésük úgy kezdődik, hogy az alkalmazásprocesszor végzi a számításigényes algoritmusok többségét. Ebből a pontból indulnak ki, majd azonosítják a szoftver azon kulcsfontosságú részeit, amelyek a központi feldolgozóegység (CPU) órajelének nagy részét fogyasztják, és ezeket a részeket HDL implementációba helyezik át. Ennek grafikus ábrázolása nagyban hasonlít az eddig bemutatottakhoz, azonban ők úgy döntöttek, hogy az Alkalmazásprogramot önálló blokkként ábrázolják, mivel az akár a Hostban (a processzorban), akár az FPGA alapú hardverben is megvalósítható.

4. ábra: Alkalmazásprogram, gazdaprocesszor és FPGA-alapú hardver – egy műholdas kommunikációs példában.

4. ábra: Alkalmazásprogram, gazdaprocesszor és FPGA-alapú hardver – egy műholdas kommunikációs példában.

Egy beviteli-kiviteli eszközöket összekapcsoló (peripheral component interconnect, PCI) interfész és a gazdaprocesszor közvetlen memória-hozzáférésének (DMA) használatával a perifériák működési teljesítménye drámaian megnövekszik. Ez leginkább a derandomizálási folyamat javításainál figyelhető meg. Amikor ezt a folyamatot a gazdaprocesszor szoftvere végezte, a rendszer valós idejű válaszában egyértelmű késések léptek fel a torlódások miatt. Az FPGA-ra való áttelepítéskor azonban a következő előnyök mutatkoztak:

- A derandomizálási folyamat valós időben, torlódások kialakulása nélkül zajlott.

- A gazdaprocesszorra háruló számítási terhek jelentősen csökkentek, és most már jobban el tudta látni a kívánt naplózási szerepet.

- Az egész rendszer teljes teljesítményét megnövelték.

Mindezt egy ASIC-kel járó költségek nélkül, élvezve a programozható logika rugalmasságát [5]. A műholdas kommunikáció jelentős kihívásokkal jár, és ez a megközelítés bizonyíthatóan megfelel ezeknek a követelményeknek, és továbbra is biztosítja a tervezési rugalmasságot.

Járműipari infotainment példa

Az autókba épített szórakoztató rendszerek jelenlétére vagy hiányára az igényes felhasználók odafigyelnek. Az autóelektronika többségétől eltérően ezek az eszközök jól látható helyeken vannak, és kivételes válaszidőt és teljesítményt várnak el tőlük. A tervezők azonban gyakran szorult helyzetben vannak, mivel a jelenkori igények és a jövőbeli kívánt funkciók nagyban eltérhetnek és ez megfelelő rugalmasságot követel. Ebben a példában a jelfeldolgozás és a vezeték nélküli kommunikáció megvalósításakor jelentkező igényeket használjuk fel a társprocesszoros hardverarchitektúra erősségeinek kiemelésére.

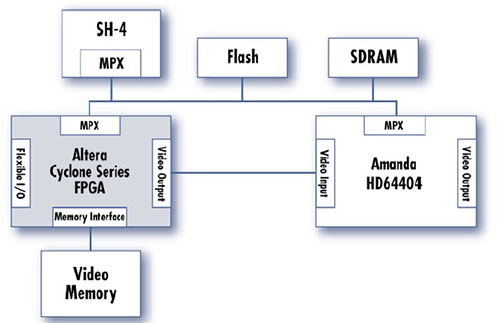

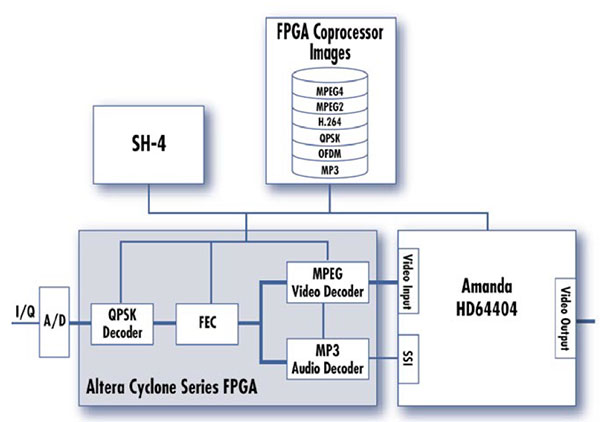

Az egyik legelterjedtebb autóipari szórakoztatórendszer-architektúrát a Delphi Delco Electronics Systems vállalat fejlesztette ki. Ez az architektúra egy SH-4 MCU-t használt egy társ ASIC-vel, a Hitachi HD64404 Amanda perifériájával. Ez az architektúra képes volt kielégíteni az autóipari piac alapvető szórakoztató funkcióinak több mint 75%-át, azonban nem volt képes a videófeldolgozási alkalmazások és a vezeték nélküli kommunikáció kezelésére. Az FPGA-nak ebbe a meglévő architektúrába való beépítésével további rugalmasság és képességek adhatók hozzá ehhez a már meglévő tervezési megközelítéshez.

5. ábra: FPGA társprocesszoros infotainment architektúra, 1. példa.

5. ábra: FPGA társprocesszoros infotainment architektúra, 1. példa.

Az 5. ábrán látható architektúra alkalmas mind a videofeldolgozásra, mind a vezeték nélküli kommunikáció kezelésére. A DSP-funkcióknak az FPGA-ba való áthelyezésével az Amanda processzor rendszerirányítási szerepet tölthet be, és felszabadul egy vezeték nélküli kommunikációs stack megvalósítására. Mivel mind az Amanda, mind az FPGA hozzáfér a külső memóriához, gyors adatcsere valósítható meg a rendszer processzorai és más elemei között.

6. ábra: FPGA társprocesszoros infotainment architektúra, 2. példa.

6. ábra: FPGA társprocesszoros infotainment architektúra, 2. példa.

A 6. ábrán látható második infotainment rendszer kiemeli az FPGA azon képességét, hogy mind a bejövő nagysebességű analóg adatok kezelését, mind a videoalkalmazásokhoz szükséges tömörítést és kódolást megoldja. Valójában mindezek a funkciók áthelyezhetők az FPGA-ba, és a párhuzamos feldolgozás révén mindezek valós időben kezelhetők.

Az FPGA-nak egy meglévő hardverarchitektúrába történő beépítésével a már bizonyítottan jól működő meglévő hardver rugalmas és jövőbiztos maradhat. A társprocesszoros architektúra még a meglévő rendszereken belül is olyan lehetőségeket biztosít a tervezők számára, amelyek egyébként nem állnának rendelkezésre [6].

A gyors prototípuskészítés előnyei

A gyors prototípuskészítési folyamat lényege, hogy a feladatok párhuzamos végrehajtása, a programhibák és a tervezési problémák gyors azonosítása, valamint az adat- és jelútvonalak validálása révén a termékfejlesztési terület jelentős részét igyekszik lefedni, különösen egy-egy projekt kritikus útvonalán belül. Ahhoz azonban, hogy ez a folyamat valóban ésszerűsített, hatékony eredményeket hozzon, elegendő szakértelemmel kell rendelkezni a szükséges projektterületeken.

Hagyományosan ez azt jelenti, hogy kell egy hardvermérnök, egy beágyazott szoftver- vagy DSP-mérnök és egy HDL-mérnök. Ma már rengeteg interdiszciplináris szakember van, akik képesek lehetnek több szerepkör betöltésére, azonban ezen fejlesztések koordinálása még mindig jelentős projektköltséggel jár.

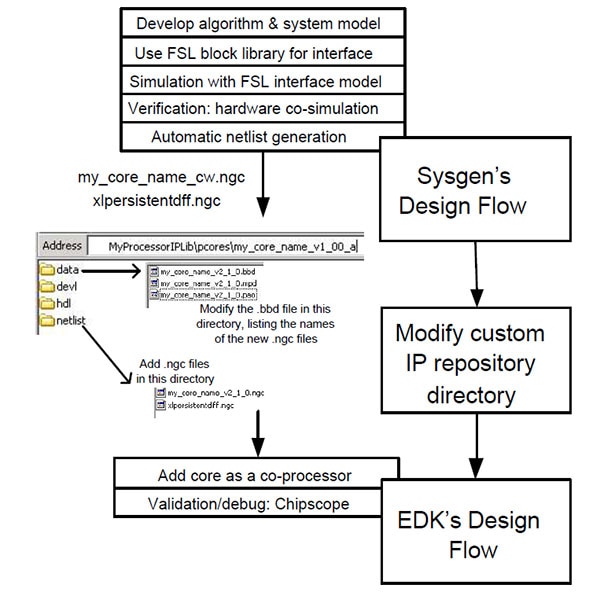

Az An FPGA based rapid prototyping platform for wavelet coprocessors című tanulmányukban a szerzők amellett érvelnek, hogy a társprocesszoros architektúra használatával mindezen szerepeket egyetlen DSP mérnök hatékonyan és eredményesen be tudja tölteni. Ehhez a tanulmányhoz a csapat a MATLAB Simulink eszközén belül kezdte meg a kívánt DSP-funkciók tervezését és szimulációját. Ezt két elsődleges céllal tették: 1) szimulációval ellenőrizték a kívánt teljesítményt, és 2) alapként szolgált, amelyhez a jövőbeli tervezési döntéseket viszonyíthatták, és amelyre hivatkozni lehetett.

A szimuláció után a kritikus funkciókat azonosították, és különböző magokra osztották – ezek olyan soft-core komponensek és processzorok, amelyek szintetizálhatók egy FPGA-n belül. A munka során a legfontosabb lépés az volt, hogy meghatározzák e magok és komponensek közötti interfészt, és összehasonlítsák az adatcsere teljesítményét a kívánt, szimulált teljesítménnyel. Ez a tervezési folyamat szorosan illeszkedik a Xilinx beágyazott rendszerek tervezési folyamatához, és az alábbi 7. ábra foglalja össze.

7. ábra: Megvalósítás tervezési folyamata.

7. ábra: Megvalósítás tervezési folyamata.

A rendszernek szintetizálható magokra való felosztásával a DSP mérnök a jelfeldolgozási lánc legkritikusabb aspektusaira koncentrálhat. Nem kell hardver- vagy HDL-szakértőnek lennie ahhoz, hogy különböző soft-core processzorokat vagy komponenseket módosítson, azok útvonalán módosítson vagy azokat implementálja az FPGA-n belül. Amíg a tervező tisztában van az interfésszel és az adatformátumokkal, addig teljes mértékben ellenőrizheti a jelútvonalakat, és finomíthatja a rendszer teljesítményét.

Empirikus eredmények – a diszkrét koszinusz transzformáció esettanulmánya

Az empirikus eredmények nemcsak a társprocesszoros architektúra által biztosított rugalmasságot igazolták a beágyazott rendszerek tervezői számára, hanem jól szemléltették a modern FPGA-eszközökkel elérhető teljesítménynövelő lehetőségeket is. Előfordulhat, hogy az alábbi fejlesztések más hardverarchitektúrák esetében egyáltalán nem lehetségesek, vagy pedig kevésbé hatékonyak. Számításigényes algoritmusként a diszkrét koszinusz transzformációt (DCT) választottuk, és a C-alapú implementációról a HDL-alapú implementációra való áttérés állt ezen eredmények középpontjában. A DCT-t azért választottuk, mert ezt az algoritmust használják a digitális jelfeldolgozásban mintafelismerésre és szűrésre [8]. Az empirikus eredmények egy laboratóriumi gyakorlaton alapultak, amelyet a szerző és munkatársai végeztek el a Xilinx Alliance Partner minősítésnek a 2020-2021-es időszakra való megszerzése érdekében.

Erre a következő eszközöket használtuk fel:

- Vivado HLS v2019

- Az értékeléshez és a szimulációhoz használt eszköz az xczu7ev-ffvc1156-2-e volt

A C-alapú megvalósításból kiindulva a DCT algoritmus két 16 bites számokból álló tömböt fogad el; az „a” tömb a DCT bemeneti tömbje, a „b” tömb pedig a DCT kimeneti tömbje. Az adatszélesség (DW) tehát 16, a tömbökben lévő elemek száma (N) pedig 1024/DW, azaz 64. Végül a DCT-mátrix mérete (DCT_SIZE) 8-ra van állítva, ami azt jelenti, hogy egy 8 x 8-as mátrixot használunk.

A cikk előfeltevése szerint az algoritmus C-alapú implementálása lehetővé teszi a tervező számára az algoritmus gyors fejlesztését és funkcionalitásának validálását. Bár ez egy fontos szempont, ennél a validációnál a funkcionalitásnak nagyobb súlya van, mint a végrehajtási idő. Ez a súlyozás megengedett, mivel az algoritmus végső megvalósítása FPGA-ban történik majd, ahol a hardveres gyorsítás, a ciklusok kibontása és más technikák könnyen elérhetők.

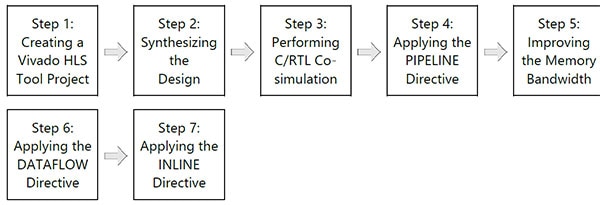

8. ábra: A Xilinx Vivado HLS tervezési folyamata.

8. ábra: A Xilinx Vivado HLS tervezési folyamata.

Miután a Vivado HLS eszközben egy projektként létrehoztuk a DCT kódot, a következő lépés a tervnek az FPGA-ban való implementálásához szükséges szintézis megkezdése. Ez az a következő lépés, ahol az algoritmus MCU-ról FPGA-ra történő áthelyezésének néhány legjelentősebb előnye nyilvánvalóvá válik – referenciaként ez a lépés megegyezik a „Rendszer irányítása a mikrovezérlővel” mérföldkővel, amelyet fentebb tárgyaltunk.

A modern FPGA-eszközök számos optimalizálást és fejlesztést tesznek lehetővé, amelyek nagymértékben növelik az összetett algoritmusok teljesítményét. Az eredmények elemzése előtt néhány fontos fogalmat kell tisztáznunk:

- Késleltetés – a ciklus összes iterációjának végrehajtásához szükséges órajelciklusok száma [10]

- Intervallum – az órajelciklusok száma, mielőtt a ciklus következő iterációja megkezdi az adatfeldolgozást [11]

- BRAM – Block Random Access Memory

- DSP48E – DSP slice az UltraScale architektúrához

- FF - Flip-flop

- LUT - Hivatkozási táblázat (Look-up Table)

- URAM - Unified Random-Access Memory (egyetlen tranzisztorból is állhat)

|

||||||||||||||||||||||||||||||||||||||||

1. táblázat: FPGA-val történő algoritmusvégrehajtási optimalizálás eredményei (késleltetés és intervallum).

|

2. táblázat: FPGA-val történő algoritmusvégrehajtási optimalizálás eredményei (erőforrás-kihasználás).

Alapértelmezett

Az alapértelmezett optimalizálási beállítás a C-alapú algoritmus változatlan átültetése szintetizálható HDL-be. Semmilyen optimalizálás sem engedélyett, és ez teljesítményreferenciaként használható a többi optimalizálási lehetőségek jobb megértéséhez.

Pipeline belső hurok

A PIPELINE utasítás utasítja a Vivado HLS-t a belső hurkok kibontására, hogy az új adatok feldolgozása már akkor megkezdődhessen, amikor a meglévő adatok még a csővezetékben vannak. Így az új adatok feldolgozásának megkezdése előtt nem kell megvárni a meglévő adatok feldolgozásának befejezését.

Pipeline külső hurok

A PIPELINE utasításnak a külső hurokra való alkalmazásával a külső hurok műveletei hajtódnak végre adatcsatornás feldolgozással (pipelining). A belső hurkok műveleteinek végrehajtása azonban párhuzamosan történik. Mind a késleltetési idő, mind az intervallumok ideje felére csökken, ha ezt közvetlenül a külső hurokra alkalmazzuk.

Array partition

Ez az utasítás a ciklusok tartalmát tömbökre képezi le, és így a tömbökön belül az egyes elemekhez való memória-hozzáférést ellaposítja. Ez több RAM-ba kerül, de az algoritmus végrehajtási ideje a felére csökken.

Dataflow

Ez az utasítás lehetővé teszi a tervező számára, hogy megadja az egyes bemeneti olvasások közötti órajelciklusok célszámát. Ez az utasítás csak a legfelső szintű függvények esetében támogatott. Csak az ezen a szinten lévő ciklusok és függvények részesülnek ezen utasítás előnyeiből.

Inline

Az INLINE utasítás minden belső és külső hurkot ellaposít. A sor- és oszlopfolyamatok mostantól egyidejűleg is végrehajthatók. A szükséges órajelciklusok számát a lehető legkisebbre csökkentjük, még akkor is, ha ez több FPGA-erőforrást igényel.

Összegzés

A társprocesszoros hardverarchitektúra olyan nagy teljesítményű platformot biztosít a beágyazott rendszerek tervezői számára, amely a fejlesztés során és a termékbevezetést követően is megőrzi a tervezési rugalmasságot. Az algoritmusok első, C vagy C++ nyelven történő validálásával a folyamatok, az adat- és jelútvonalak, valamint a kritikus funkciók viszonylag rövid idő alatt ellenőrizhetők. Ezután a processzorigényes algoritmusoknak a társprocesszoros FPGA-ba való átültetésével a tervező kiélvezheti a hardveres gyorsítás és a modulárisabb kialakítás előnyeit.

Ha az alkatrészek elavulnak vagy optimalizálásra van szükség, ugyanaz az architektúra lehetőséget biztosít ezen változtatások megvalósítására. Új MCU-k és új FPGA-k illeszthetők a kialakításba, miközben az interfészek viszonylag érintetlenek maradhatnak. Továbbá, mivel mind az MCU, mind az FPGA helyszínen frissíthető, a felhasználó-specifikus módosítások és optimalizálások a helyszínen és távolról is elvégezhetők.

Zárszóként, ez az architektúra az MCU-kkal lehetséges fejlesztési sebességet és ezen alkatrészek rendelkezésre állásának előnyösségét ötvözi az FPGA teljesítményével és bővíthetőségével. A minden fejlesztési szakaszban rendelkezésre álló optimalizációs lehetőségek és teljesítménynövelések révén a társprocesszoros architektúra a legigényesebb követelményeknek is megfelel – mind a mai, mind a jövőbeli tervekben.

Disclaimer: The opinions, beliefs, and viewpoints expressed by the various authors and/or forum participants on this website do not necessarily reflect the opinions, beliefs, and viewpoints of DigiKey or official policies of DigiKey.