Alacsony jitterű nagyfrekvenciás órajelek gyors létrehozása offset hurok modul segítségével

Contributed By DigiKey's North American Editors

2021-08-04

A műszer- és mérőrendszerek tervezőinek alacsony jitterű és zavarmentes jelekre van szükségük ahhoz, hogy az egyre szigorúbb vevői követelmények teljesítéséhez szükséges jel-zaj viszonyt (SNR) vagy hibavektornagyságot (EVM) biztosítsák. Ugyanakkor jelentős nyomás nehezedik rájuk, hogy csökkentsék a kártyák helyigényét, valamint a tervezési költségeket és a bonyolultságot. Ez utóbbi a fejlesztési idő lerövidítése szempontjából kritikus fontosságú, hogy az egyre szűkülő piacrajutási időablakoknak való megfelelés lehetséges legyen.

A számos alkalmazási probléma megoldása érdekében a mérnököknek a műszer- és mérőrendszerek órajelmegoldásai területén a hagyományosan egyedi, diszkrét konstrukciókról át kell állniuk az integráltabb megoldásokra. Ennek a folyamatnak fontos lépése az integrált offset fáziszárt hurok (PLL) használata. Ez lehetővé teszi a hagyományos feszültségvezérelt oszcillátor-jel (VCO) frekvenciájának felfelé konvertálását, miközben lényegében megtartja a fix külső helyi oszcillátor (LO) jitterszintjét és fáziszaját.

Ez a cikk az offset hurkoknak az iparági legalacsonyabb integrált fáziszaj elérésében játszott szerepét tárgyalja. Példaként bemutatja az Analog Devices ADF4401A egytokos rendszerű offset hurok (TL SiP) eszközét, és szemlélteti, hogy hogyan felel meg az a teljesítménykövetelményeknek a 10 femtoszekundum (fs) rms alatti, széles sávú integrált jitter értékű kimeneti jelének és a zavaró komponensek csillapítására szolgáló fokozott elválasztásnak köszönhetően, miközben kielégíti a tervezők integrációra, költségre, bonyolultságra, illetve piacra kerülési időre vonatkozó igényeit is.

A hagyományos PLL és az offset hurok működése

Az offset hurok elsődleges célja egy bemeneti referenciajelhez rögzített olyan kimeneti jel előállítása, amely a hagyományos PLL-ekhez képest jelentősen csökkentett sávon belüli fáziszajjal rendelkezik.

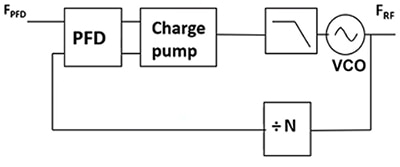

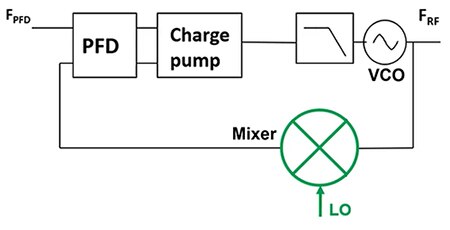

A standard PLL egy visszacsatolt rendszer, amely egy fázis-frekvencia detektort (PFD), töltőszivattyú (charge pump) típusú feszültségátalakítót, aluláteresztő szűrőt (LPF), VCO-t és egy visszacsatoló N frekvenciaosztót tartalmaz (1. ábra).

1. ábra: A standard PLL egy alacsonyabb frekvenciájú (FPFD) referenciajelhez zár és a (FRF) kimeneti frekvenciát hozza létre. (Kép: Bonnie Baker)

1. ábra: A standard PLL egy alacsonyabb frekvenciájú (FPFD) referenciajelhez zár és a (FRF) kimeneti frekvenciát hozza létre. (Kép: Bonnie Baker)

A PFD összehasonlítja a bemeneti referenciajel és a visszacsatolt jel fázisát, és a kettő közötti fázishibával arányos impulzusok sorozatát generálja. A töltőszivattyú fogadja a PFD impulzusait és átalakítja őket áramforrás- vagy áramnyelő-impulzusokká, amelyek pedig felfelé vagy lefelé hangolják a VCO frekvenciáját. Az LPF a nagyfrekvenciás összetevők eltávolításával a VCO számára használható feszültséggé alakítja az impulzusokat. A VCO kimeneti jelét az N osztón keresztül visszatáplálják a PFD blokkba a hurok zárásának érdekében.

Az 1. ábra frekvenciaátviteli függvénye az 1. egyenlet segítségével számítható ki:

![]() 1. egyenlet

1. egyenlet

Ahol FRF a kimeneti frekvencia

N a visszacsatoló osztó osztási aránya (lehet egész vagy tört szám)

FPFD a PFD frekvenciája

Az 1. ábra sávon belüli zajküszöbét a 2. egyenlet adja meg

![]() 2. egyenlet

2. egyenlet

Ahol FOMPLL a PLL sávon belüli fáziszaj-küszöbérték mutatója (FOM)

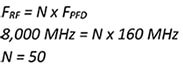

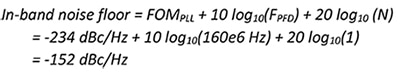

Vegyünk egy példát, ahol a sávon belüli fáziszaj-küszöbérték mutató (FOM) -234 dB/Hz; a PFD frekvencia (FPFD) 160 MHz és a kimeneti frekvencia (FRF) 8 GHz.

Erre a rendszerre vonatkozóan az N értékének kiszámításához az 1. egyenletet kell használni:

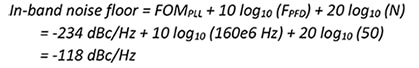

A 2. egyenlet a sávon belüli zajküszöb kiszámítására használatos:

A fenti számításban az N osztó nagymértékben hozzájárul a teljes sávon belüli zajküszöbhöz, mértéke 20 log10 (50), ami 34 dB-nek felel meg. Egy kisebb N-érték csökkentené a sávon belüli zajküszöböt; azonban a kimeneti frekvencia is csökkenne. Hogyan hozzunk tehát létre magas kimeneti frekvenciát alacsonyabb hurokerősítés (N) mellett?

2. ábra: A példában szereplő standard PLL esetében a visszacsatoló osztó zaja 34 dB-lel (20 log10(N)) nagyobb sávon belüli zajt eredményez az alsó, sárga színű görbéhez képest, amelyre vonatkozóan N = 1. (Kép: Bonnie Baker)

2. ábra: A példában szereplő standard PLL esetében a visszacsatoló osztó zaja 34 dB-lel (20 log10(N)) nagyobb sávon belüli zajt eredményez az alsó, sárga színű görbéhez képest, amelyre vonatkozóan N = 1. (Kép: Bonnie Baker)

A megoldás erre a problémára az, ha az N-osztót egy lefelé konvertáló keverőfokozattal helyettesítjük (3. ábra).

3. ábra: Az offset hurok a hagyományos visszacsatoló osztó helyett keverőt használ a VCO frekvenciájának a PFD frekvenciára történő lekonvertálására. (Kép: Bonnie Baker)

3. ábra: Az offset hurok a hagyományos visszacsatoló osztó helyett keverőt használ a VCO frekvenciájának a PFD frekvenciára történő lekonvertálására. (Kép: Bonnie Baker)

A 3. ábrán a keverő helyettesíti az N visszacsatoló osztót, így a hurok erősítése 1 (N=1). Ez a művelet nagymértékben csökkenti a visszacsatoló hurok hozzájárulását a sávon belüli zajküszöbhöz. A sávon belüli zaj számításához az N értéke most 1. A 2. egyenlet alapján a módosított rendszer sávon belüli zajküszöbe a következő:

A sávon belüli zaj új értéke 34 dBc/Hz-es javulást mutat.

A 3. ábrán a keverő egy rendkívül alacsony zajszintű helyi oszcillátortól (LO), az úgynevezett offset LO-tól függ. A hurok zárt állapotához FLO ± FRF értékének meg kell egyeznie FPFD értékével.

Az offset hurok architektúra révén az offset LO fáziszaja nagyon fontos szerepet játszik a legjobb teljesítőképesség elérésében az RF kimeneten. Ezen oknál fogva a mérnökök jellemzően feszültségvezérelt akusztikai felületihullám (SAW) szűrőkön, oszcillátorokon (VCSO), fésűjel-generátorokon, vagy dielektromos rezonátoros oszcillátorokon (DRO) alapuló offset LO-t terveznek. MEGJEGYZÉS: Az offset LO tervezésével kapcsolatos támogatásért forduljon az Analog Devices céghez.

Az offset hurokhoz kapcsolódó nehézségek

Egy alacsony zajszintű offset hurok létrehozása hagyományosan számos áramköri blokk megvalósítását jelenti, aminek eredménye egy összetett, általában terjedelmes és korlátozottan rugalmas elrendezés. Ezen kívül a teljes áramkört validálni kell, továbbá hozzá kell igazítani a megvalósítandó feladathoz. Például az egyik fő tervezési probléma a helyi oszcillátor (LO) jelének szórása az RF kimeneti jelre (LO-RF elválasztás). Ez jelentős probléma a mérnökök számára. A hagyományos elrendezések esetében a mérnökök általában több tervezési változatot ellenőriznek az optimális működés és a megfelelő elválasztás elérése érdekében.

A 3. ábra bemutatja, hogy az ADF4401A jelű eszköz hogyan integrálja a főbb áramköri blokkokat, hogy teljes mértékben a feladathoz igazított megoldást nyújtson és kiküszöbölje az offset hurkok tervezésében a működéshez és az elválasztáshoz kapcsolódó hagyományos nehézségeket. Ez a programozható megoldás lehetővé teszi a mérnökök számára, hogy már az első próbálkozáskor optimalizált működést érjenek el, és csökkentsék a piacra kerülési időt.

Az ADF4401A kiértékelése

Az ADF4401A-t úgy tervezték, hogy egy 62,5 MHz és 8 GHz közötti RF sávban működő frekvenciagenerációs megoldásként segítse a mérnököket a nagy teljesítőképességű műszerek piacra kerülési idejének csökkentésében. Lefelé konvertáló keverő alkalmazásával az ADF4401A nagyon alacsony sávon belüli zajjal rendelkezik, 100 Hz és 100 MHz közötti integrált ~9 fs széles sávú jitter értékkel. Az ADF4401A-ban alkalmazott tervezési és elrendezési technikák tipikusan 90 dBc zavarmentes dinamikatartományt tesznek lehetővé. A tok 18 x 18 x 2,018 mm-es mérete a hagyományos diszkrét kialakításhoz képest jelentősen csökkenti a helyigényt.

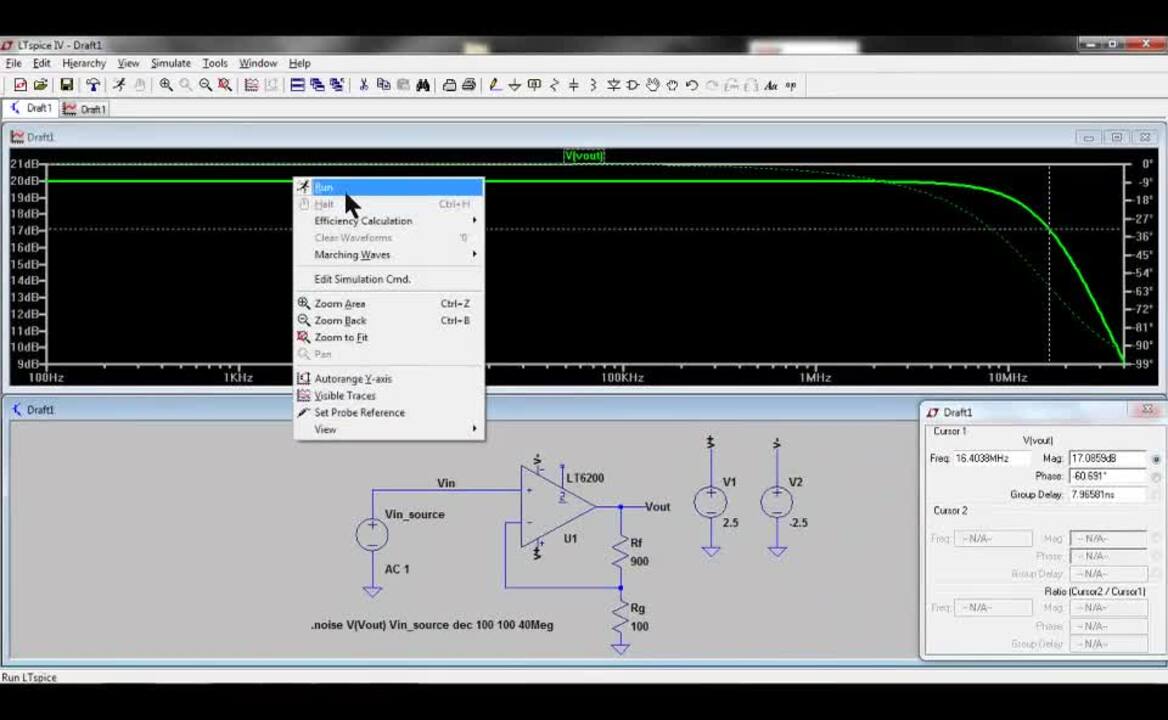

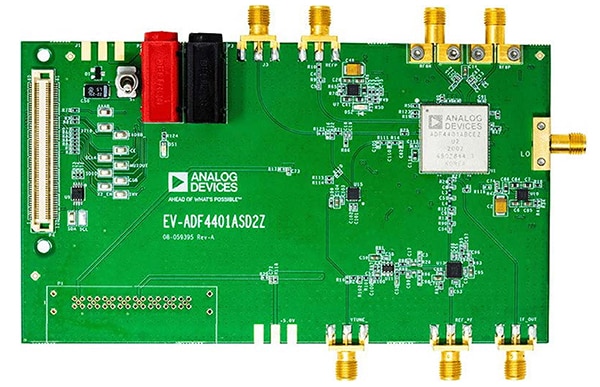

A DCM3623TA5N53B4T70 képességeinek kiértékeléséhez a tervezők rendelkezésére áll az EV-ADF4401ASD2Z fejlesztői kártya (4. ábra). A kártya tartalmaz egy teljes offset hurkot, beleértve a külső PFD-t (HMC3716), egy aktív szűrőt (LT6200) és egy multiplexert (ADG1609).

4. ábra: Az ADF4401A offset hurok modulhoz készült EV-ADF4401ASD2Z fejlesztői kártya külső PFD-t, USB interfészt és feszültségszabályozókat tartalmaz. (Kép: Analog Devices)

4. ábra: Az ADF4401A offset hurok modulhoz készült EV-ADF4401ASD2Z fejlesztői kártya külső PFD-t, USB interfészt és feszültségszabályozókat tartalmaz. (Kép: Analog Devices)

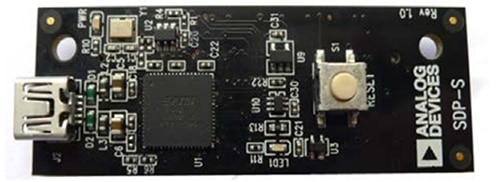

Az EV-ADF4401ASD2Z részei az integrált VCO-val rendelkező ADF4401A TL SiP, a hurokszűrő (5 MHz), a PFD, az USB interfész és a feszültségszabályozók. Ezen kívül az EV-ADF4401ASD2Z-hez szükség van az EVAL-SDP-CS1Z (SDP-S) rendszerdemonstrációs platform (SDP) (soros) vezérlőkártyára is (5. ábra). A kártya USB kapcsolatot biztosít a PC és az EV-ADF4401ASD2Z között, utóbbi ezáltal programozható. Az EV-ADF4401ASD2Z készlet a vezérlőkártyát nem tartalmazza.

5. ábra: Az EVAL-SDP-CS1Z (vagy SDP-S) vezérlőkártyára az EV-ADF4401ASD2Z és a PC között a programozáshoz szükséges USB kapcsolat biztosítása érdekében van szükség. (Kép: Analog Devices)

5. ábra: Az EVAL-SDP-CS1Z (vagy SDP-S) vezérlőkártyára az EV-ADF4401ASD2Z és a PC között a programozáshoz szükséges USB kapcsolat biztosítása érdekében van szükség. (Kép: Analog Devices)

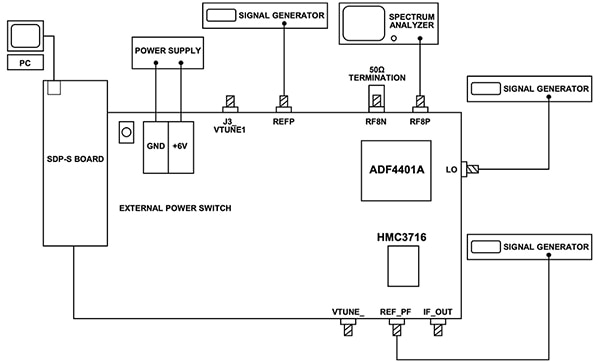

A 6. ábra az EV-ADF4401ASD2Z rendszer fizikai csatlakozásait mutatja be. A hozzá tartozó elemző - vezérlő - kiértékelő (ACE) szoftver vezérli a TL SiP funkcióit. A tápellátást egy külső 6 V-os tápegység biztosítja.

6. ábra: Az EV-ADF4401ASD2Z beállítási diagramja mutatja az ADF4401A kiértékeléséhez szükséges berendezéseket és kapcsolatokat, beleértve az SDP-S vezérlőkártyát, a PC-t, a tápegységet, a jelgenerátorokat és a spektrumanalizátort. (Kép: Analog Devices)

6. ábra: Az EV-ADF4401ASD2Z beállítási diagramja mutatja az ADF4401A kiértékeléséhez szükséges berendezéseket és kapcsolatokat, beleértve az SDP-S vezérlőkártyát, a PC-t, a tápegységet, a jelgenerátorokat és a spektrumanalizátort. (Kép: Analog Devices)

A fejlesztői kártyával való használatra javasolt berendezés egy Windows PC-ből, egy spektrumanalizátorból vagy jelforrás-analizátorból, valamint három jelgenerátorból áll.

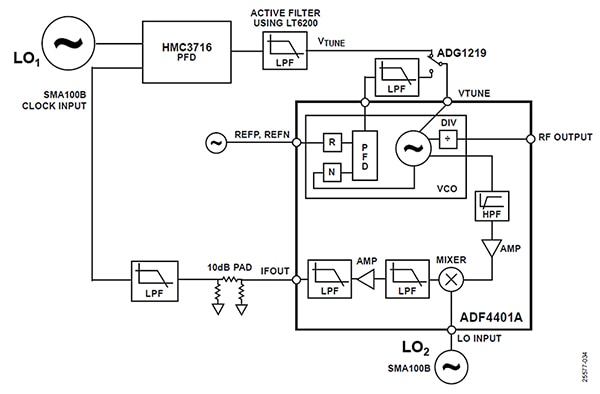

Az EV-ADF4401ASD2Z blokkdiagramján látható az ADF4401A modul, valamint az Analog Devices HMC3716 PFD, az LT6200 műveleti erősítő és az ADG1219 SPDT kapcsoló (7. ábra).

7. ábra: Az EV-ADF4401ASD2Z fejlesztői kártya blokkdiagramján az AD4401A offset hurkot támogató kulcsfontosságú alkatrészek láthatók. (Kép: Analog Devices)

7. ábra: Az EV-ADF4401ASD2Z fejlesztői kártya blokkdiagramján az AD4401A offset hurkot támogató kulcsfontosságú alkatrészek láthatók. (Kép: Analog Devices)

Alapvetően fontos nagy frekvenciákon működőképes PFD-t használni, mivel így minimálisra csökkenthető a frekvenciaosztók iránti igény, ezek ugyanis ronthatják a sávon belüli zajválaszt. Az Analog Devices HMC3716 jelű eszközének fázisösszehasonlító funkciója 1,3 GHz-ig működik, ami ideális az ADF4401A IF tartományában való használatra. Mivel egy ilyen áramkör a frekvencia és a fázis összehasonlítására is képes, nincs szükség további áramkörökre, amelyek a frekvenciát a kívánt kimeneti frekvenciára húzzák. A HMC3716 szerepel külső PFD-ként az offset hurok zárásához. A HMC3716 nagyfrekvenciás működési tartománya és ultraalacsony fáziszajszintje nagy sávszélességű hurokszűrők tervezését teszi lehetővé.

A 7. ábrán az LT6200 műveleti erősítő LPF beállításban csillapítja a nagyfrekvenciás zavarokat, a rendszer offset hurokját pedig az ADG1219 kapcsoló zárja.

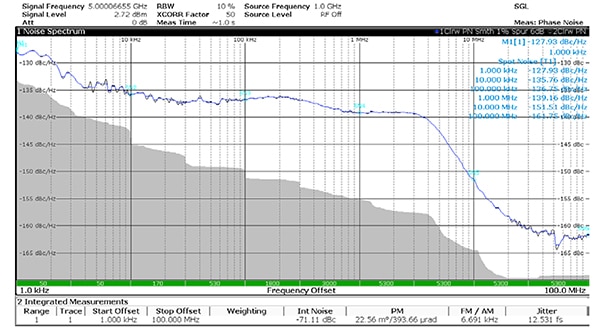

Az EV-ADF4401ASD2Z kiértékelő elrendezés a 8. ábrán látható, sávon belüli zajra és jitterre vonatkozó mérési eredményeket adja.

8. ábra: Egyoldalsávos fáziszaj 5 GHz-es kimeneten, HMC3716 által biztosított 500 MHz-es külső referencia és 4,5 GHz-es külső helyi oszcillátor (LO) esetén. (Kép: Analog Devices)

8. ábra: Egyoldalsávos fáziszaj 5 GHz-es kimeneten, HMC3716 által biztosított 500 MHz-es külső referencia és 4,5 GHz-es külső helyi oszcillátor (LO) esetén. (Kép: Analog Devices)

A 8. ábrán az LO2 és a HMC3716 bemenete egy SMA100B RF és mikrohullámú jelgenerátor. A fejlesztői kártya LO2 jelének sávon belüli zaja körülbelül -135 dBc/Hz, ami kis, legfeljebb 300 kHz offset esetén látható. Az LO2, az ADF4401A modul, a HMC3716 PFD és a hurokszűrő sávon belüli zaja körülbelül -140 dBc/Hz. A belső fáziszaj 5 MHz és 50 MHz között jelentkezik, és az elrendezés zajküszöbe körülbelül -160 dBc/Hz. Ezek együttesen összesen 12,53 fs rms jitter értéket eredményeznek.

Összegzés

A nagy sebességű műszerrendszerek a kimeneti adatok sértetlensége érdekében rendkívül alacsony jitterű órajeleket igényelnek. A mérnökök számára kihívás jelent olyan megfelelő eszközöket találni, amelyekből nagy sebességű, GHz-es nagyságrendű órajelrendszer építhető fel. Az ADF4401A offset hurok jelentősen leegyszerűsíti az órajelrendszer összeállításához szükséges eszközök kiválasztását, és olyan kompakt modult bocsát rendelkezésre, amely magasabb frekvenciákon alacsony jittert biztosít, ugyanakkor csökkenti a helyigényt, a költségeket és a piacra kerülési időt.

Disclaimer: The opinions, beliefs, and viewpoints expressed by the various authors and/or forum participants on this website do not necessarily reflect the opinions, beliefs, and viewpoints of DigiKey or official policies of DigiKey.