Különféle funkcionális és biztonsági követelményeknek való megfelelés többmagos processzorokkal

Contributed By DigiKey's North American Editors

2020-10-01

Az autóipari, ipari, robotikai, épületfelügyeleti és más kritikus beágyazott rendszerszintű alkalmazásoknak egyre különfélébb munkaterheléseknek kell megfelelniük, az egyszerű kisfogyasztású, valós idejű adatfigyeléstől kezdve az ember-gép kapcsolatra (HMI-re) szolgáló többképernyős, grafikus kijelzős legkorszerűbb multimédiás rendszerekig. Ezen széleskörű funkcionális követelményeknek való megfelelésen túlmenően szigorú biztonsági előírásoknak is meg kell felelniük, alacsonyabb költségek és helyigény mellett, optimalizált fogyasztás-teljesítmény egyensúllyal.

E gyakran olykor ellentmondó követelmények teljesítéséhez a fejlesztők előtt egészen eddig mindig két út állt: vagy le kellett mondaniuk funkcionális lehetőségekről, vagy pedig a tervezést és a gyártást bonyolító olyan komponenseket kellett alkalmazniuk, amelyek ahhoz kellettek, hogy megfeleljenek többek között a grafikai, a munkabiztonsági és az adatbiztonsági követelményeknek. A fejlesztőknek igazából egy átfogó megoldásra van szükségük, amely széleskörűen alkalmazható az ezen követelményeknek megfelelő különböző eszközöket tartalmazó kritikus beágyazott rendszerszintű alkalmazásoknál.

Ez a cikk a kritikus beágyazott rendszerek tervezésének fejlődését ismerteti röviden. Ezután bemutatja, hogyan használhatók a fejlesztőkkel szembeni kihívások teljesítésére az NXP Semiconductors többmagos alkalmazásprocesszorai, amelyeket speciálisan arra fejlesztettek ki, hogy támogassák a széleskörű funkcionalitást és megfeleljenek a biztonsági minősítésű feladatok követelményeinek, amelyek listája igen gyorsan bővül.

A beágyazott rendszerek tervezési szempontjainak fejlődése

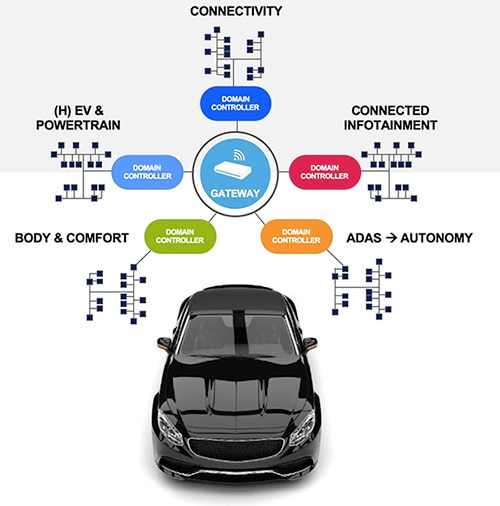

A beágyazott eszközök szerepe korábban kimerült csupán abban, hogy támogattak néhány korlátozott számú rendszerfunkciót, de mára ezt már javarészt felváltotta a széles lehetőségeket biztosító eszközök iránti igény. Például az ipari rendszerekben használt intelligens szerszámok és berendezések HMI felületeinek fejlődése miatt olyan processzorokra van szükség, amelyek amellett, hogy megfelelnek a hagyományos ipari valós idejű követelményeknek, optimalizált grafikus megjelenítésre is képesek. Hasonlóképpen, az autóipari rendszereknél a funkcionális doménklaszterekből és átjárókból álló hierarchikus architektúrák felé történő elmozdulás olyan processzorok kifejlesztését követeli, amelyek teljes mértékben képesek megfelelni ezeknek a követelményeknek (1. ábra).

1. ábra A hierarchikusabb gépjárműrendszer-architektúrák megjelenése integráltabb, skálázható processzoros megoldások iránti igényt teremtett. (Kép: NXP Semiconductors)

1. ábra A hierarchikusabb gépjárműrendszer-architektúrák megjelenése integráltabb, skálázható processzoros megoldások iránti igényt teremtett. (Kép: NXP Semiconductors)

Az egyes funkcionális egységeken belül, egyre nagyobb igény van az egyre kifinomultabb feladatok végzésére, és ez folyamatosan emeli a kívánt teljesítmény és a beépített lehetőségek határát. A HUD (heads-up display) technológia megjelenése miatt például olyan megoldásokra van szükség, amelyek a járművezetők számára biztosítani képesek a létfontosságú grafikus információk folyamatos áramlását. Ezek a következő generációs kijelzők mellett a vezetéssegítő rendszerek iránti fokozott igény további követelményeket támaszt, például megfelelő interfészeket kamerákhoz való kapcsolódáshoz és az álmosságot felismerő szoftverek precíz és rendkívül gyors futtatását.

A rendszerek folyamatos fejlődésével, egyre sürgetőbb szükség mutatkozik a nagyfokúan integrált, skálázható megoldásokra, hogy a tervezők meg tudjanak felelni az egyre változatosabb követelményeknek, a minimumra csökkentve ugyanakkor a helyigényt, a költségeket és a komplexitást. Az NXP i.MX 8 alkalmazásprocesszor-családjának használatával a fejlesztők egy olyan kompatibilis processzorplatformra támaszkodhatnak, amely rendelkezik mindazokkal a képességekkel és azzal teljesítménnyel, ami a széleskörű alkalmazási követelmények kielégítéséhez kell. Az i.MX 8 családon belül az NXP i.MX 8X sorozat készült arra, hogy kielégítse a középkategóriás autóipari és ipari rendszerekben használható biztonsági minősítésű processzorok elérhetősége iránti sürgető igényt.

Különféle munkaterhelések kezelése többmagos architektúrával

Az egyik nehézség, amellyel a fejlesztők az eszközöknek az autóipari és ipari rendszerekbe történő beépítésekor szembesülnek maga az, hogy rengeteg követelménynek meg kell felelni. Ott, ahol a fejlesztők azt várnák, hogy vagy csak a valós idejű, vagy a magas szintű alkalmazás-feldolgozási munkaterhelési problémákkal kellene foglalkozniuk, az intelligens alrendszerek iránti igénynek köszönhetően ez a két egymástól jelentősen eltérő számítástechnikai problémakör már egyesült. A fejlesztőknek ezért egyre inkább olyan megoldásokra van szükségük, amelyek egyaránt megbízható valós idejű válaszadásra és villámgyors alkalmazás-végrehajtásra is képesek, mindeközben megfelelve a funkcionális biztonsági követelményeknek.

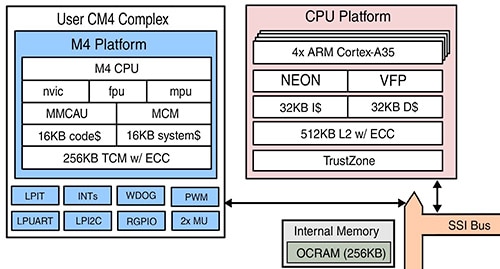

Az NXP valós idejű képeségekkel rendelkező, nagyteljesítményű adatfeldolgozásra tervezett, és alacsony energiafogyasztású i.MX 8X sorozatú processzorai teljes mértékben kihasználják a bonyolult többmagos CPU-architektúrát a különféle számítási feladatok elvégzésére (2. ábra).

2. ábra Az NXP i.MX 8X sorozata egy Arm Cortex-M4 (CM4) beágyazott processzort és több Arm Cortex-A35 alkalmazásprocesszort tartalmazó többmagos architektúrára épül, a kevert szoftveres munkaterhelések elvégezhetősége érdekében. (Kép: NXP Semiconductors)

2. ábra Az NXP i.MX 8X sorozata egy Arm Cortex-M4 (CM4) beágyazott processzort és több Arm Cortex-A35 alkalmazásprocesszort tartalmazó többmagos architektúrára épül, a kevert szoftveres munkaterhelések elvégezhetősége érdekében. (Kép: NXP Semiconductors)

Az általános célú, valós idejű feldolgozási feladatokhoz az i.MX 8X-ek egy lebegőpontos egységet (FPU-t), memóriavédelmi egységgel (MPU-t), memóriatérképezett kriptográfiai gyorsító egységet (MMCAU-t) és egyéb vezérlő modulokat (MCM-et) tartalmazó Arm Cortex-M4 (CM4) processzort tartalmaznak. A külső perifériák, például a szenzorok és működtető elemek támogatásához a User CM4 complex blokkban egy beágyazott vektoros megszakításkezelő (Nested Vector Interrupt Controller – NVIC) van kombinálva egy átfogó interfész- és modulkészlettel, többek között egy kisfogyasztású periodikus megszakításgeneráló időzítővel (Low-Power Periodic Interrupt Timer – LPIT), impulzusszélesség modulációval (PWM) és az autóipari és ipari alkalmazásokban általában szükséges egyéb funkciókkal. A hibajavító kódolással (ECC-vel) felvértezett gyorsítótárak és az extrém gyors elérésű memória (TCM) a minimumra csökkentik a külső memóriára való hagyatkozást, gyors végrehajtást biztosítanak és javítják az adathibákat.

Az alkalmazási munkaterhelések gyors végrehajtásához a CPU platform több energiahatékony Arm Cortex-A35 alkalmazásprocesszort (AP-t) tartalmaz: két AP-t a 8DualXPlus típusú processzorokban (például MIMX8UX6AVLFZAC), és négy AP-t a 8QuadXPlus típusú processzorokban (például MIMX8QX6AVLFZAC). A speciálisan az utasítások (I$) és adatok (D$) feldolgozására szánt gyorsírótár mellett a CPU platform tartalmaz egy osztott-hozzáférésű 512 kilobájtos L2 gyorsírótárat is ECC hibajavítással.

A felépítésben lévő Arm Cortex-A35 magok a szoftveres kompatibilitást és a skálázható teljesítményt egyaránt biztosítják, támogatva a 32 bites visszamenőleges kompatibilitást és a 64 bites működést is. A számításigényes algoritmusok, például a jelfeldolgozás és a gépi tanulás végrehajtásának további gyorsítása érdekében az Arm Cortex-A35 processzorok lebegőpontos adatfeldolgozásra (VFP) képesek, és eszköztáruk része az Arm NEON SIMD (egy utasítás - több adat) utasításkészlet is. A képfeldolgozáshoz, a számítógépes látáshoz és a gépi tanuláshoz szükséges szoftverek működésének felgyorsításához az Arm Compute Library könyvtárában az Arm processzorokra és GPU-kra optimalizált funkciók találhatók, valamint a nyílt forráskódú Ne10 C könyvtár is rendelkezik az Arm rendszerekre optimalizált funkciókkal a számításigényes műveletekhez.

Az elsődleges CPU-k tehermentesítése célra rendelt motorokkal

A User CM4 complex blokkon és az Arm Cortex-A35 többmagos CPU platformon kívül az architektúra további dedikált motorokat tartalmaz a multimédiás alkalmazások támogatására. A hang- és videojelek feldolgozásához szükséges digitális jelfeldolgozó (DSP) mellett az architektúra egy integrált GPU-t és video-feldolgozó egységet (VPU-t) is tartalmaz. Az eszköz GPU-ja támogatja a standard grafikus könyvtárakat, négy különálló négykomponensű lebegőpontos vektor (vec4) felhasználásával, 16 végrehajtási egységgel és egy nagy teljesítményű, kétdimenziós bit-blit motorral gyorsítva fel a műveleteket. A VPU a népszerű videoformátumok kezeléséért felelős, 4Kp30 dekódolási (progresszív, 30 Hz) és 1080p30 kódolási teljesítménnyel. Emellett, a chipen lévő dedikált kijelzővezérlő-blokk akár három független kijelzőt is képes vezérelni.

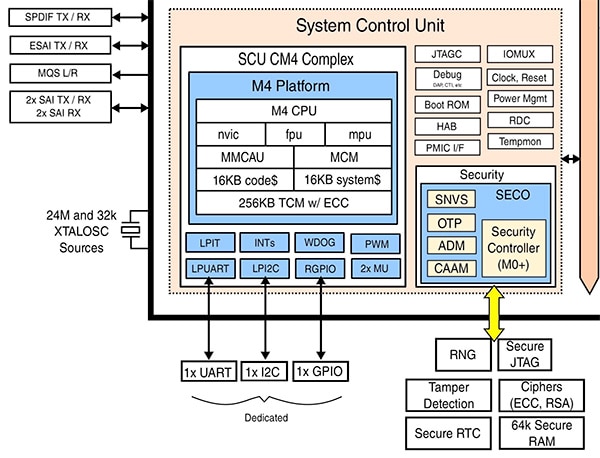

A teljesítmény további maximalizálása érdekében az i.MX 8X architektúra más integrált processzormagokat is tartalmaz, amelyeket arra terveztek, hogy mentesítsék az elsődleges CPU-platformokat a rendszerkezelési és biztonsági szolgáltatások futtatása során általában felmerülő további munkaterheléstől. A rendszerirányításhoz az architektúra rendszervezérlő egysége (SCU) egy integrált CM4 complex blokkot tartalmaz, amely azonos a User CM4 complex blokkal, de amely kizárólag az SCU műveleteit kezeli és a fejlesztők számára nem elérhető (3. ábra).

3. ábra Az NXP i.MX 8X processzorokba mélyen beágyazott, és a fejlesztők számára nem elérhető SCU a dedikált Arm Cortex-M4 (CM4) alrendszert használja arra, hogy tehermentesítse az eszköz fő processzorait a rendszerkezelési feladatoktól. (Kép: NXP Semiconductors)

3. ábra Az NXP i.MX 8X processzorokba mélyen beágyazott, és a fejlesztők számára nem elérhető SCU a dedikált Arm Cortex-M4 (CM4) alrendszert használja arra, hogy tehermentesítse az eszköz fő processzorait a rendszerkezelési feladatoktól. (Kép: NXP Semiconductors)

Az áramellátás, az órajel és más belső funkciók vezérlésével együtt normál működés esetén az SCU vezérli az lábkivezetés kiosztását (pin multiplexing) és a bemeneti/kimeneti csatornák vezérlésére használt áram erősségét. A User CM4 complex blokk és az Arm Cortex-A35 alkalmazásprocesszorok nem tudnak közvetlenül hozzáférni ezekhez a különféle alacsony szintű hardveres funkciókhoz. Ehelyett az SCU feladata módot biztosítani ezeknek a lehetőségeknek a kihasználására, tehát például a nem használt tápellátási területek kikapcsolásához és más hasonló funkciók végrehajtásához a User CM4-en vagy AP-ken futó szoftvereknek egyszerűen meg kell hívniuk az SCU firmware adott alkalmazás-programozási felületi (API) funkcióit. Ha az adott tápellátási területet például egy másik processzor is használja, az SCU egyszerűen nyugtázza a kikapcsolási kérelmet, de a területet áram alatt fogja tartani, amíg az a másik processzor is egy kikapcsolási kérelmet nem küld.

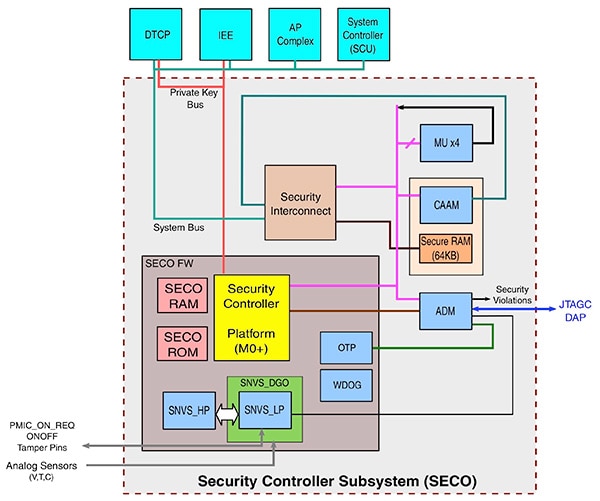

Az i.MX 8X-ek számos biztonsági funkcióinak kezeléséhez egy másik dedikált processzor található az eszköz SECO (biztonságvédelmi) alrendszerében. A SECO alrendszeren belül egy integrált, kisfogyasztású Arm Cortex-M0+ processzor van, amelynek firmware-je hardveralapú biztonsági funkciókat támogat, beleértve egy privát buszt a biztonságos kulcsokhoz való hozzáféréshez, egyszer programozható (OTP) memóriát és egy további, a magánadatok vagy rövid életű kulcsok tárolására szolgáló biztonságos nem felejtő tárhelyet (SNVS-t) (4. ábra).

4. ábra Az NXP i.MX 8X biztonságvédelmi (SECO) alrendszerén belül egy privát kulcs-hozzáférési buszra és több hardveregységre támaszkodó dedikált, kisfogyasztású Arm Cortex-M0+ processzor kezeli a biztonsági műveleteket, az adatok biztonságos tárolásához, a kriptográfia gyorsításához és hitelesített hibakereséshez. (Kép: NXP Semiconductors)

4. ábra Az NXP i.MX 8X biztonságvédelmi (SECO) alrendszerén belül egy privát kulcs-hozzáférési buszra és több hardveregységre támaszkodó dedikált, kisfogyasztású Arm Cortex-M0+ processzor kezeli a biztonsági műveleteket, az adatok biztonságos tárolásához, a kriptográfia gyorsításához és hitelesített hibakereséshez. (Kép: NXP Semiconductors)

Ezeken az alapvető biztonsági mechanizmusokon túl a SECO alrendszer az ADM (Authentified Debug Module) moduljával koordinálja a szabotázsok észleléséhez és a biztonságos hibaelhárításhoz szükséges biztonsági műveleteket. A biztonságos végrehajtáshoz az integrált Cryptographic Acceleration and Assurance Module (CAAM) hardveres biztonsági modul egy komplett biztonsági algoritmus-készlettel kezelhető, beleértve a szimmetrikus és aszimmetrikus kriptográfiát, a hash függvényeket és egy véletlenszám-generátort (RNG).

Normál működés esetén az eszköz feldolgozóegységei, beleértve az SCU-t, az AP-ket és a Digital Transport Content Protection (DTCP) gyorsítót, a SECO biztonsági vonalait használják a CAAM funkciók elérésére a rendszerbuszon keresztül. A CAAM-on keresztüli közvetlen memória-hozzáférésen (DMA) kívül a SECO dedikált Cortex-M0+ processzora nem képes hozzáférni a rendszerbuszhoz. Ehelyett védett belső kapcsolatokat használ a perifériák, a biztonságos véletlen hozzáférésű memória (RAM), az írásvédett memória (ROM) és a privát kulcs-hozzáférési busz eléréséhez.

Az i.MX 8X processzorokál a DTCP gyorsítóval együtt ennek a privát kulcs-hozzáférési busznak központi szerepe van a menet közbeni titkosítás és visszafejtés támogatásában. Ilyenkor a titkosított tárolóból/-ba való olvasás/írás közben a biztonsági processzor a saját erőforrásait felhasználva biztosítja az eszköz Inline Encryption/Decryption Engine (IEE) modulja számára szükséges privát kulcsokat a kérelmet küldő processzor, DMA vezérlő vagy I/O eszköz részvétele nélkül.

Az eszköz Cortex-A35 processzoraiba integrált Arm TrustZone technológiára építve a SECO alrendszer a biztonságos indítási folyamat közben is együttműködik az SCU-val. Ebben a folyamatban az SCU értelmezi az indítási beállításokat, konfigurálja az indítási forrásokat, és betölti a rendszerindító image fájlokat a belső vagy a külső memóriába. Ezzel együtt, a SECO alrendszer a betöltésük után, de még a végrehajtásuk előtt a kriptográfiai funkcióival hitelesíti az aláírt firmware image fájlokat.

A kritikus fontosságú kijelzők és irányítási funkciók védelme

Míg a különféle munkaterhelések hatékony és biztonságos feldolgozása igen fontos, ugyanolyan létfontosságú megőrizni az üzemkritikus alkalmazások (mint amilyenekkel például az autóipari és az ipari rendszerekben találkozhatunk) kulcsfontosságú képességeit is. Az NXP i.MX 8X család ötvözi az adatfeldolgozási képességeket azokkal a biztonsági minősítésű funkciókkal, amelyek ezeknek a kritikus követelményeknek a teljesítéséhez szükségesek.

A processzorcsalád tagjaiba épített biztonság számos szinten megjelenik, többek között már a gyártás kezdetén is, a rendszer megbízhatóságát növelő FD-SOI (Fully-Depleted Silicon-On-Insulator) előállítási technológiával. Mivel a rendszerbiztonságnak megbízható alapokon kell nyugodnia, a TrustZone-kompatibilis AP-k, a SECO alrendszer és a biztonságos rendszerindítási funkciók kombinációja egy olyan biztonságos környezetet teremt, ahol a biztonságosságot fenyegető veszélyek elháríthatók.

Ugyanakkor az a lehetőség, hogy az időkritikus feladatok az User CM4 complex blokkal függetlenül kezelhetők, valamint hogy a kritikus rendszerfeladatok átruházhatók az SCU-ra és a SECO-ra segít biztosítani, hogy az üzemkritikus alkalmazások funkciói változó adatfeldolgozási terhelés mellett is elérhetőek maradjanak. Sőt, a SafeAssure technológiájával ezt az elvet az NXP a létfontosságú kijelzők támogatására is kiterjeszti, azzal, hogy egy ASIL B szintű hardveres kijelző-meghibásodási (failover) útvonal van integrálva az i.MX 8X eszközökbe. A SafeAssure biztosítja azt, hogy a rendszer átkapcsoljon, és a felhasználóknak automatikusan egy tartalék útvonalról kapott kép jelenjen meg, ha az eszköz adatintegritási- vagy GPU-hibát észlel. Ez a háttérben rendelkezésre álló kép biztosítja, hogy a kritikus információk még az elsődleges kijelző meghibásodása esetén is elérhetőek maradjanak.

Az i.MX 8X-alapú rendszereknél a biztonsági alkalmazások támogatása a memóriahozzáférésre is kiterjed. A támogatott memória interfészek közül az i.MX 8X eszközök 8 bites ECC-t biztosítanak az alacsony fogyasztású Double Data Rate 3 (DDR3L) memóriák esetében. Az L2 cache ECC-jével együtt (lásd ismét a 2. ábrát) ez a DDR3L ECC képesség a SIL 3-as biztonságintegritási szintnek is megfelel. Az i.MX 8X architektúra az ECC-támogatást a külső flash tárolóeszközökre is kiterjeszti. Ebben az esetben egy integrált Bose, Ray-Chaudhuri, Hocquenghem (BCH) kódoló és dekódoló modul 62 bites ECC-t biztosít, amely 2-20 egybites hibát képes kijavítani az ezekből a tárolóeszközökből kiolvasott adatblokkok esetén.

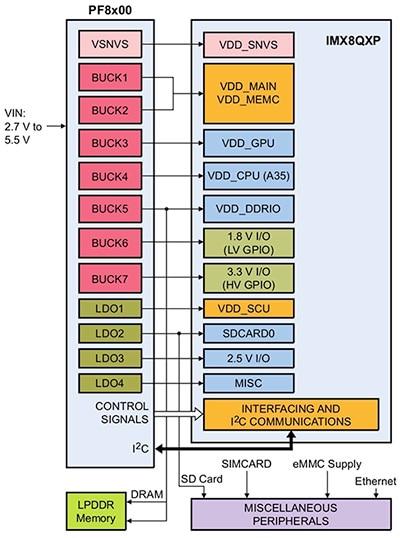

Az i.MX 8X alapú alkalmazások kontrollált elindítása

Mint minden ebbe az osztályba tartozó processzor esetében, egy i.MX 8X alapú architektúra implementálásakor is körültekintő figyelmet kell fordítani a szigorú áramellátási követelményekre, ideértve a kritikus bekapcsolási sorrendeket is. Az i.MX 8X eszközök bekapcsolásához négy különböző tápellátási csoportnál kell egymás után vagy egyidejűleg üzemi szintre emelni a feszültséget, kezdve az SVNS alrendszerrel, folytatva az SCU-val, az I/O-kkal és a memória interfészekkel, majd befejezve az eszköz többi részével. Az NXP PF8x00 áramellátás-kezelő integrált áramköreivel (PMIC) ez a követelmény egyszerűen teljesíthető, mivel azokban megtalálható minden olyan feszültségáramkör és vezérlőjel, ami az i.MX 8X processzorok, valamint a külső memória és a tipikus rendszerperifériák működtetéséhez kell (5. ábra).

5. ábra Az NXP PF8x00 PMIC-kben megtalálható minden olyan feszültségáramkör és vezérlőjel, ami az i.MX 8X processzorok áramellátásának biztosításához kell. (Kép: NXP Semiconductors)

5. ábra Az NXP PF8x00 PMIC-kben megtalálható minden olyan feszültségáramkör és vezérlőjel, ami az i.MX 8X processzorok áramellátásának biztosításához kell. (Kép: NXP Semiconductors)

A saját i.MX 8X-ra épülő terveik megvalósításakor a fejlesztők használhatják a 8QuadXPlus processzorokhoz (mint amilyen az MIMX8QX6AVLFZAC) előre beprogramozott NXP MC33PF8100CCES PMIC-t. Más PF8x00 típusok (például az MC33PF8100A0ES és az MC33PF8200A0ES) is kompatibilisek az i.MX 8X processzorokkal, de nincsenek előre beprogramozva.

Biztonsági alkalmazásokhoz a PF8200 sorozatú eszközökbe, például az MC33PF8200A0ES-be, integrálva vannak az ASIL B minősítésű rendszerek támogatására kifejlesztett funkciók. A több belső figyelőáramkörrel, köztük egy dedikált kimeneti referenciafeszültség-figyelő áramkörrel együtt a PF8200 PMIC-kben egy hibakezelő kimeneti (FSOB) érintkező is van, amely arra szolgál, hogy a rendszert üzembiztos állapotban tartsa bekapcsolás vagy áramkimaradás esetén. Ezenkívül, amíg egy öntesztelő rutin az eszköz egyéb funkcióinak ellenőrzését végzi, egy beépített analóg öntesztelő (ABIST) rutin teszteli az összes feszültségfigyelést.

Habár a PF8x00 PMIC-k leegyszerűsíthetik az i.MX 8X alapú rendszerek esetében a hardvertervezést, előfordulhat, hogy egyes fejlesztőknek azonnal meg kell kezdeniük az i.MX 8X eszközök kielemzését, és be kell indítaniuk i.MX 8X alapú prototípusok gyors kifejlesztését. Az NXP MCIMX8QXP-CPU i.MX 8X Multisensory Enablement Kit (MEK) készlete egy használatra kész fejlesztői platform, amelyben egy NXP i.MX 8QuadXPlus processzor, egy NXP F8100 PMIC, 3 Gbyte RAM, egy 32 Gbyte-os beágyazott Multi-Media Controller (eMMC) memória és 64 Mbyte flash memória található. A kijelzőkkel, kamerákkal és audio rendszerekkel kompatibilis interfészek mellett a MEK-kártya az autóipari vagy ipari rendszerekben gyakran használt szenzorokból álló készletet is tartalmaz. A további összekapcsolhatósági, audio és bővítési képességekért a fejlesztők az alaprendszert az NXP opcionális MCIMX8-8X-BB alaplapjával is bővíthetik.

Összegzés

Az autóipar, az ipar, az épületfelügyelet, a HMI-k és egyre több más rendszer esetében is a feldolgozási munkaterhelés kibővült, és a hagyományosan csupán a bemenetek/kimenetek valós idejű vezérlése mellett most már egyaránt magába foglalja az előtörő és egyre elterjedtebbé váló multimédiás grafikus alkalmazás-szintű feldolgozást is. Habár mindkét típusú munkaterheléshez rendelkezésre állnak kész tervek, kevés olyan elérhető megoldás létezik, ami ki tudná elégíteni a nagy teljesítményű, energiahatékony megoldások iránti egyre növekvő igényt az autóipari és ipari rendszerekben, ahol biztonsági minősítésű tervekre van szükség.

Mint ahogy azt bemutattuk, az NXP Semiconductors többmagos processzorcsaládjának felhasználásával a fejlesztők hatékonyabban tudnak létrehozni olyan kialakításokat, amelyek egyidejűleg ezeknek a különféle követelményeknek is képesek megfelelni, de ugyanakkor könnyen méretezhetők is az egyre nagyobb teljesítmény iránti igények kielégítése érdekében.

Disclaimer: The opinions, beliefs, and viewpoints expressed by the various authors and/or forum participants on this website do not necessarily reflect the opinions, beliefs, and viewpoints of DigiKey or official policies of DigiKey.