FPGA SoC-k használata hálózatokhoz kapcsolódó valós idejű biztonságkritikus rendszerekhez

Contributed By DigiKey's North American Editors

2023-02-16

Az FPGA-k (programozható logikai kapumátrixok), a Linux-kompatibilis RISC-V mikrovezérlős (MCU) alrendszerek, a korszerű memóriaarchitektúrák és a nagy teljesítményű kommunikációs interfészek fontos eszközök a tervezők számára. Ez különösen igaz a hálózatokhoz kapcsolódó biztonságos rendszerek, a biztonságkritikus rendszerek és a kemény valós idejű determinisztikus rendszerek, például a mesterséges intelligenciára (AI) és a gépi tanulásra (ML) épülő rendszerek tervezői számára.

Ezeknek a különböző elemeknek egy biztonságos, hálózatokhoz kapcsolódni képes és determinisztikus rendszerbe történő integrálása azonban sok megoldandó problémát követelő és időigényes feladat lehet, csakúgy, mint a nagysebességű összeköttetések kiépítése a különböző rendszerelemek között. A tervezőknek memóriakezelő egységet, memóriavédelmi egységet, biztonságos rendszerindítási képességet és gigabites sebességű adó-vevőegységeket kell beépíteniük a nagysebességű hálózati kapcsolódási képesség megvalósításához. Aktív és statikus energiagazdálkodásra és túláramok szabályozására is szükség lesz a megépített konstrukcióban. Egyes konstrukcióknál a pn-átmenet hőmérsékletének (TJ) a 0 °C és +100 °C közötti bővített kereskedelmi hőmérséklet-tartományban kell lennie, míg az ipari környezetben lévő rendszereknek a -40 °C és +100 °C közötti TJ-tartományban kell működniük.

Az ilyen és más problémák megoldására a tervezők FPGA elemet tartalmazó SoC (System-on-Chip) integrált áramkörökhöz fordulhatnak, amelyek az alacsony energiafogyasztást, a magas hőelvezetési hatékonyságot és a katonai szintű biztonságot ötvözik intelligens, összekapcsolt és determinisztikus rendszerek kifejlesztéséhez.

Ez a cikk egy ilyen FPGA SoC-architektúrát tekint át, és azt, hogy az hogyan használható fel hatékonyan hálózatokhoz kapcsolódni képes és determinisztikus rendszerek megtervezésére. Ezután röviden bemutatja a feldolgozási teljesítmény/energiafogyasztás viszonyra alapuló EEMBC CoreMark-Pro teljesítménymutatót, valamint egy reprezentatív FPGA SoC teljesítményét. Áttekinti, hogyan épül be a biztonság ezekbe az FPGA SoC-kbe, és példaként bemutat néhány FPGA SoC-t a Microchip Technology-től a tervezési folyamatot felgyorsító néhány fejlesztési platformmal együtt. A cikk a MikroElektronika által gyártott bővítőkártyák rövid felsorolásával zárul, melyekkel számos kommunikációs interfész, valamint globális műholdas navigációs rendszer (GNSS) alapú helymeghatározási képesség valósítható meg.

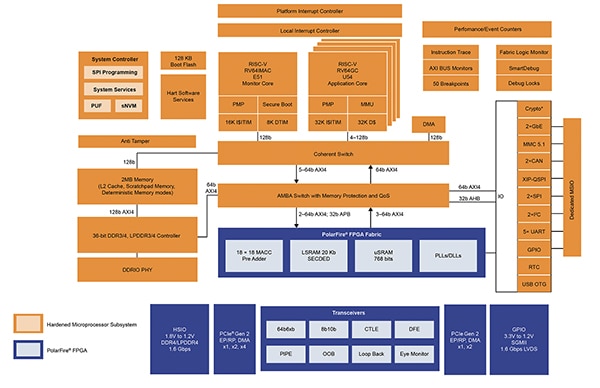

FPGA struktúrás SoC-k

Ilyen SoC (System on Chip) integrált áramkörök esetén a „chip” egy FPGA szövet, amely tartalmazza a rendszerelemeket, az FPGA-tól a fixen beágyazott (hard) FPGA-logikával megvalósított RISC-V MCU alrendszerig. Az MCU-alrendszer tartalmaz egy négymagos RISC-V MCU-klasztert, egy RISC-V monitorozó magot, egy rendszervezérlőt és egy determinisztikus 2. szintű (L2) memória alrendszert. Az ezekben a SoC-kben található FPGA akár 460K logikai elemet, akár 12,7 gigabit/másodperc sebességű adó-vevő egységeket és egyéb bemeneti/kimeneti (I/O) blokkokat tartalmaz, beleértve az általános célú I/O-t (GPIO) és a Peripheral Component Interconnect Express (PCIe) 2-t is. A teljes architektúra megtervezésekor a megbízhatóság az egyik lényeges szempont. Mindegyik memóriára vonatkozólag tartalmaz egy SECDED-alapú (single-error correction/double-error detection) hibajavító és -kezelő rendszert, differenciáláram analízist (DPA), fizikai memóriavédelmet és 128 Kbit flash boot memóriát (1. ábra).

1. ábra: Az FPGA SoC minden eleme, beleértve a RISC-V alrendszereket is az FPGA-struktúrán van megvalósítva (kép: Microchip Technology)

1. ábra: Az FPGA SoC minden eleme, beleértve a RISC-V alrendszereket is az FPGA-struktúrán van megvalósítva (kép: Microchip Technology)

A Microchip a saját Mi-V („my five”) fejlesztői környezetét kínálja RISC-V rendszerek megvalósítására, harmadik féltől származó más eszközökkel és tervezési segédeszközökkel együtt. A Mi-V arra készült, hogy felgyorsítsa a RISC-V utasításkészlet-architektúra (ISA) bevezetését a fixen beágyazott (hard) RISC-V magok és a tetszés szerint konfigurálható (soft) RISC-V magok számára. A Mi-V fejlesztői környezeten belül a következők férhetők hozzá:

- szellemi tulajdon (IP) licencek;

- hardver;

- operációs rendszerek és köztes szoftverek;

- hibakeresők, fordítók és tervezési szolgáltatások.

Az FPGA SoC-ben lévő, kemény RISC-V MCU-k számos hibakeresési képességgel rendelkeznek, mint például a passzív, futásidőben konfigurálható Advanced eXtensible Interface (AXI) és az utasítások nyomon követése. Az AXI lehetővé teszi a tervezők számára a különböző memóriákba írt vagy onnan olvasott adatok nyomon követését, és azt, hogy mikor történik az írás vagy olvasás.

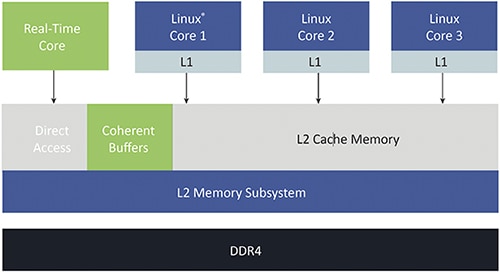

A RISC-V MCU-alrendszer működése ötfokozatú, egyutas, sorrendben működő, in-order pipeline alapú. Nem sebezhető a rendezetlen architektúrákat sújtható Spectre vagy Meltdown exploitokkal szemben. Az öt MCU mindegyike koherens a memória alrendszerrel, és determinisztikus aszimmetrikus többfolyamatos (AMP) üzemmódú valós idejű rendszerekkel és a Linux-szal kompatibilis. A RISC-V alrendszer képességei a következők (2. ábra):

- Linux és kemény valós idejű (hard real-time) műveletek futtatása;

- az L1 és az L2 determinisztikus memóriaként konfigurálható;

- DDR4 memória alrendszer;

- dinamikus utasítás-előrejelzés kikapcsolása/engedélyezése;

- in-order pipeline típusú működés.

2. ábra: A RISC-V alrendszer több processzor- és memóriaelemet tartalmaz (kép: Microchip Technology)

2. ábra: A RISC-V alrendszer több processzor- és memóriaelemet tartalmaz (kép: Microchip Technology)

Hatékonyabb feldolgozás kevesebb energiával

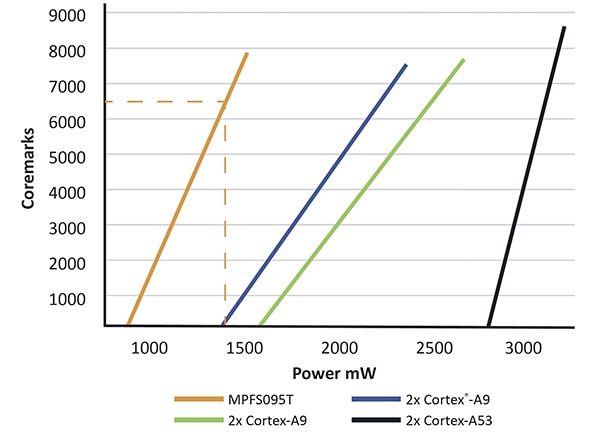

Rendszerüzemeltetési előnyeik mellett (beleértve a kemény valós idejű feldolgozás támogatását is) ezek az FPGA SoC-k rendkívül energiatakarékosak. Az EEMBC CoreMark-PRO teljesítménymutató egy iparágon belül használt szabványos mutató a beágyazott rendszerekben lévő különböző MCU-k hatékonyságának és teljesítményének összehasonlítására. Kifejezetten a hardver teljesítményének mérésére és a Dhrystone benchmark felváltására készült.

A CoreMark-PRO általi munkaterhelések sokfélék és a teljesítményjellemzők, az utasításszintű párhuzamosság és a memóriahasználat tesztelésére irányulnak, négy lebegőpontos és öt egész számokat használó általános munkaterhelés alapján. A lebegőpontos munkaterhelések közé tartozik egy LINPACK-ből származó lineáris algebrai rutin, egy gyors Fourier-transzformáció, egy neurális háló algoritmus a minták kiértékelésére, valamint a Livermore ciklusok benchmarkjának továbbfejlesztett változata. A JPEG tömörítés, egy XML-elemző, a ZIP tömörítés és egy 256 bites biztonságos hash algoritmus (SHA-256) képezi az egész számos munkaterhelésének alapját.

Ezen SoC FPGA-k MPFSO95T típusai, mint például az MPFS095TL-FCSG536E, akár 6500 pontos CoreMark eredményre is képesek 1,3 wattos fogyasztás mellett (3. ábra).

3. ábra: Az MPFS095T FPGA SoC (narancssárga görbe) 6500 pontos CoreMark teljesítményt nyújt 1,3 watt fogyasztással (kép: Microchip Technology)

3. ábra: Az MPFS095T FPGA SoC (narancssárga görbe) 6500 pontos CoreMark teljesítményt nyújt 1,3 watt fogyasztással (kép: Microchip Technology)

Biztonsági megfontolások

Az FPGA SoC-k használata biztonságkritikus és kemény valós idejű alkalmazási esetekben a magas energiahatékonyság és a nagy teljesítményű feldolgozási képességek mellett komoly biztonságot is igényel. Ezen FPGA SoC-k alapvető biztonsági funkciói közé tartozik a differenciáláram analízisnek (DPA) ellenálló bitfolyam-programozás, egy valódi véletlenszám-generátor (TRNG) és egy fizikailag másolhatatlan funkció (PUF). Tartalmazzák továbbá a szabványos és a felhasználó által meghatározott biztonságos rendszerindítási képességet, a fizikai memória védelmét, amely a gép jogosultsági állapotának megfelelő memória-hozzáférési korlátozásokat biztosít, beleértve a gépi, felügyelői vagy felhasználói üzemmódokat, valamint a Meltdown és Spectre támadásokkal szembeni védettséget.

A biztonság az ellátási lánc menedzsment biztonságosságával kezdődik, beleértve a hardveres biztonsági modulok (HSM) használatát a waferek (félvezetőszeletek) tesztelése és a tokozások során. A 768 bájtos, digitális aláírással rendelkező x.509-es FPGA-tanúsítvány használata, amely minden FPGA SoC-be be van ágyazva, növeli az ellátási lánc biztonságosságát.

Ezek az FPGA SoC-k számos chipen belüli hamisításérzékelőt tartalmaznak a biztonságos és megbízható működéshez. Manipuláció észlelése esetén a rendszer egy manipulációs jelzést ad ki, amely lehetővé teszi a rendszer számára, hogy szükség szerint reagáljon. Néhány a rendelkezésre álló manipulációérzékelők közül:

- feszültségfigyelők;

- hőmérséklet-érzékelők;

- órajelhiba- és órajelfrekvencia-érzékelők;

- aktív JTAG érzékelő;

- aktív mesh érzékelő.

A biztonságot tovább erősíti a 256 bites Advanced Encryption Standard (AES-256) használata, a szimmetrikus blokkos titkosítású correlation power attack (CPA) típusú támadások elleni intézkedések, az adatok integritását biztosító integrált kriptográfiai kivonatolási képességek, a kulcstárolásra szolgáló integrált PUF, valamint az, hogy az FPGA-struktúra és az összes chipen lévő memória nullázható.

Példák FPGA SoC-kra

A Microchip Technology a fenti képességeket és technológiákat a PolarFire FPGA SoC chipjeikben egyesíti, amelyek többféle sebességi fokozatú, hőmérsékleti besorolású és különböző tokméretű változatokkal állnak a tervezők rendelkezésére, 25K és 460K közötti logikai elemet tartalmazó megoldásokhoz. Négy hőmérsékleti fokozat áll rendelkezésre (minden esetben a TJ-re vonatkozólag): a 0 °C ... +100 °C közötti kiterjesztett kereskedelmi, a -40 °C ... +100 °C közötti ipari, a -40 °C ... +125 °C közötti autóipari és a -55 °C ... +125 °C közötti katonai tartomány.

A tervezők választhatnak a standard sebességfokozatú eszközök vagy a 15%-kal gyorsabb -1 sebességfokozatú eszközök közül. Ezek az FPGA SoC-k 1,0 volton is üzemeltethetők a legalacsonyabb fogyasztáshoz, vagy 1,05 volton, ami nagyobb teljesítményt biztosít. Többféle méretű tokozásban kaphatók, többek között 11 x 11 mm-es, 16 x 16 mm-es és 19 x 19 mm-es méretben.

Olyan alkalmazási esetekhez, ahol szélesebb kereskedelmi hőmérsékleti tartományban való normál sebességű működésre és 254K logikai elemre van szükség egy 19 x 19 mm-es tokozásban, akkor a tervezők az MPFS250T-FCVG484EES-t használhatják. Az egyszerűbb megoldásokhoz, amelyekhez elegendő 23K logikai elem, a tervezők számára rendelkezésre áll az MPFS025T-FCVG484E, amely szintén kibővített kereskedelmi hőmérsékletű üzemmóddal és szabványos sebességi fokozattal rendelkezik, 19 x 19 mm-es tokozásban. A 254K logikai elemmel rendelkező MPFS250T-1FCSG536T2-t nagy teljesítményigényű autóipari rendszerekhez tervezték, és a -40 °C ... +125°C közötti működési hőmérséklettartományban, -1 sebességi fokozatban 15%-kal gyorsabb órajelet biztosítanak, kompakt, 16 x 16 mm-es, 0,5 mm-es osztástávolságú, 536 forraszgolyós tokozásban (4. ábra).

4. ábra: Az autóipari hőmérséklettartományra tervezett MPFS250T-1FCSG536T2-t egy 16 x 16 mm-es, 536 forraszgolyós, 0,5 mm-es osztásávolságú tokozásban forgalmazzák (kép: Microchip Technology)

4. ábra: Az autóipari hőmérséklettartományra tervezett MPFS250T-1FCSG536T2-t egy 16 x 16 mm-es, 536 forraszgolyós, 0,5 mm-es osztásávolságú tokozásban forgalmazzák (kép: Microchip Technology)

Fejlesztői platform FPGA SoC-khoz

A PolarFire FPGA SoC-ket tartalmazó rendszerek tervezésének felgyorsítására a Microchip az MPFS-ICICLE-KIT-ES PolarFire SoC Icicle kit készletét kínálja, amely lehetővé teszi az ötmagos Linux-kompatibilis RISC-V mikroprocesszoros alrendszer feltérképezését alacsony fogyasztású, valós idejű végrehajtással. A készlet tartalmaz egy ingyenes Libero Silver licencet, amely a konstrukciók kiértékeléséhez kell. Egyetlen programozási nyelven keresztül nyújt programozási és hibakeresési funkciókat.

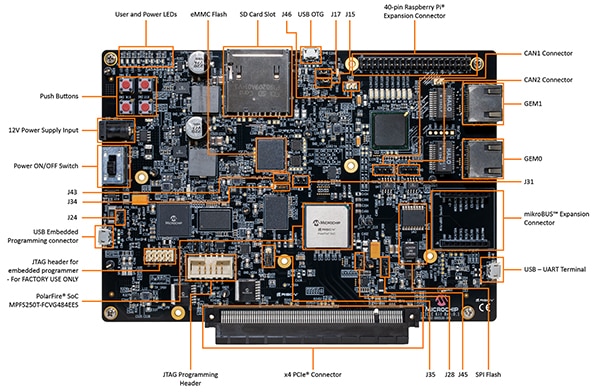

Ezek az FPGA SoC-k mellé a VectorBlox gyorsító szoftverfejlesztő készlet (SDK) is társul támogató elemeként, amely alacsony fogyasztású, kisméretű AI/ML alkalmazási eseteket tesz lehetővé. A hangsúly a tervezési folyamat egyszerűsítésén van, hogy a tervezőknek ne kelljen rendelkezniük korábbi FPGA-tervezési tapasztalatokkal. A VectorBlox gyorsító szoftverfejlesztő készlet lehetővé teszi a fejlesztők számára, hogy energiatakarékos neurális hálózatokat programozzanak C vagy C++ nyelven. Az Icicle-készlet számos olyan funkcióval rendelkezik, amelyek átfogó fejlesztési környezetet biztosítanak, beleértve egy többsávos áramellátás érzékelő rendszert a különböző áramszintek felügyeletéhez, PCIe root portot és chipre integrált memóriákat (beleértve az LPDDR4, QSPI és eMMC Flash-t) a Linux és a Raspberry Pi futtatásához, valamint mikroBUS bővítőportokat számos vezetékes és vezeték nélküli csatlakozási lehetőséghez, továbbá olyan funkcionális bővítéseket, mint a GNSS-alapú helymeghatározási képesség (5. ábra).

5. ábra: Ez az átfogó FPGA SoC fejlesztőkörnyezet Raspberry Pi (jobbra fent) és mikroBUS (jobbra lent) bővítőkártyákhoz való csatlakozókat tartalmaz (kép: Microchip Technology)

5. ábra: Ez az átfogó FPGA SoC fejlesztőkörnyezet Raspberry Pi (jobbra fent) és mikroBUS (jobbra lent) bővítőkártyákhoz való csatlakozókat tartalmaz (kép: Microchip Technology)

Bővítőkártyák

Néhány példa a mikroBUS bővítőkártyákra:

A MIKROE-986 segítségével CAN-busz alapú csatlakoztathatóság adható hozzá az alapeszközhöz soros perifériás interfész (SPI) használatával.

A MIKROE-1582 lehetővé teszi az MCU és egy RS-232 busz közötti kapcsolat létrehozását.

A MIKROE-989 RS422/485 kommunikációs buszhoz való csatlakozást tesz lehetővé.

A MIKROE-3144 támogatja az LTE Cat M1 és NB1 technológiákat, így megbízható és egyszerű csatlakozási képességet biztosít 3GPP-technológiás IoT-eszközökhöz.

A MIKROE-2670 GNSS-funkciót biztosít a GPS és a Galileo konstellációk, valamint a BeiDou vagy a GLONASS egyidejű vételével, ami nagy helymeghatározási pontosságot jelent gyenge jelek vagy a városi kanyonokra jellemző interferenciával telített helyzetekben.

Összegzés

A tervezők FPGA SoC-khez fordulhatnak, hálózatokhoz kapcsolódó, biztonságkritikus és kemény valós idejű determinisztikus rendszerek fejlesztésekor. Az FPGA SoC-k széles skálát kínálnak különböző rendszerelemekből, beleértve egy FPGA-struktúrát, egy nagy teljesítményű memóriákat tartalmazó RISC-V MCU alrendszert, nagy sebességű kommunikációs interfészeket és számos biztonsági funkciót. A tervezők számára az indulás megkönnyítése érdekében minden szükséges elemet tartalmazó fejlesztői kártyák és környezetek állnak rendelkezésre, beleértve a különböző típusú és szabványú kommunikációs és helymeghatározási funkciók megvalósításához használható bővítőkártyákat is.

Ajánlott olvasnivaló

Disclaimer: The opinions, beliefs, and viewpoints expressed by the various authors and/or forum participants on this website do not necessarily reflect the opinions, beliefs, and viewpoints of DigiKey or official policies of DigiKey.